DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

310 of 344

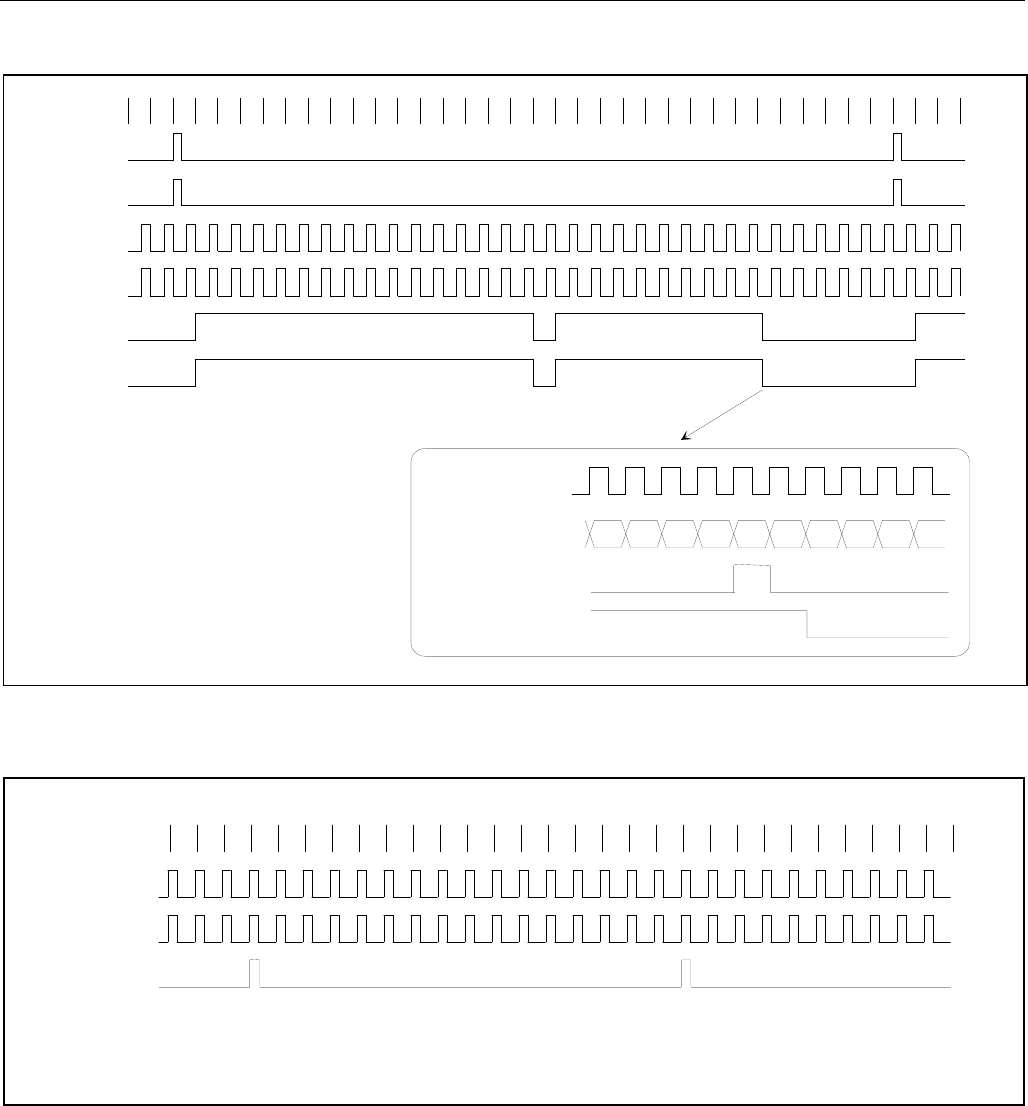

Figure 12-24. G.802 Timing, E1 Mode Only

12345678910111213141516171819202122232425262728293031031 32

TS #

RSYNC

TSYNC

RCHCLK

TCHCLK

RCHBLK

TCHBLK

CHANNEL 26

CHANNEL 25

LSB

MSB

RCLKO / RSYSCLK

TCLKT / TSYSCLK

RSERO / TSERI

RCHCLK / TCHCLK

RCHBLK / TCHBLK

120

NOTE: RCHBLK OR TCHBLK PROGRAMMED TO

PULSE HIGH DURING TIME SLOTS 1 THROUGH 15,

17 THROUGH 25, AND BIT 1 OF TIME SLOT 26.

Figure 12-25. Transmit-Side Timing

12345 67891011 12

1

TSSYNC

FRAME#

TSYNC

TSYNC

13

14 15 16

12345

14 15 16

678910

2

NOTE 1: TSYNC IN FRAME MODE (TR.IOCR1.2 = 0).

NOTE 2: TSYNC IN MULTIFRAME MODE (TR.IOCR1.2 = 1).

NOTE 3: THIS DIAGRAM ASSUMES BOTH THE CAS MF AND THE CRC4 MF BEGIN WITH THE TAF FRAME.