DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

242 of 344

Register Name:

TR.LBCR

Register Description:

Loopback Control Register

Register Address:

4Ah

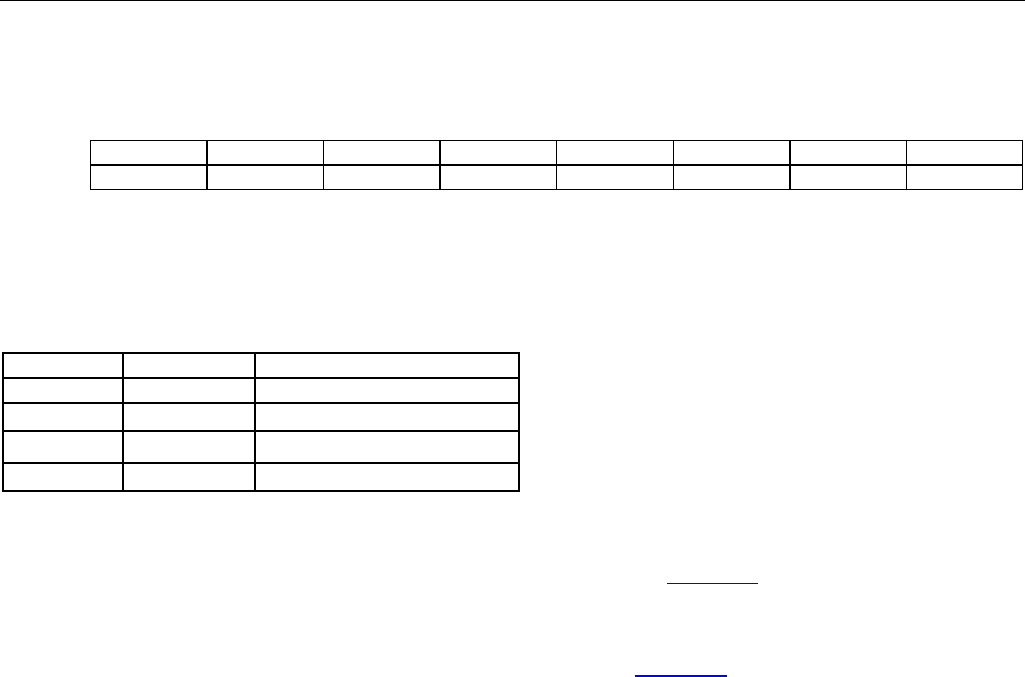

Bit # 7 6 5 4 3 2 1 0

Name — — — LIUC LLB RLB PLB FLB

Default 0 0 0 0 0 0 0 0

Bit 4: Line Interface Unit Mux Control (LIUC). This is a software version of the LIUC pin. When the LIUC pin is

connected high, the LIUC bit has control. When the LIUC pin is connected low, the framer and LIU are separated

and the LIUC bit has no effect.

0 = LIU internally connected to framer.

1 = LIU disconnected from framer. Use TPOSI/TNEGI/TDCLKI/RPOSI/RNEGI/RDCLKI pins

LIUC Pin LIUC Bit Condition

0 0 LIU and framer separated

0 1

LIU and framer separated

1 0

LIU and framer connected

1 1

LIU and framer separated

Bit 3: Local Loopback (LLB). When this bit is set to 1, data continues to be transmitted as normal through the

transmit side of the transceiver. Data being received at RTIP and RRING are replaced with the data being

transmitted. Data in this loopback passes through the jitter attenuator. See

Figure 6-3 for more details.

Bit 2: Remote Loopback (RLB). When this bit is set to 1, data input by the RPOSI and RNEGI pins is transmitted

back to the TPOSO and TNEGO pins. Data continues to pass through the receive-side framer of the transceiver as

it would normally. Data from the transmit-side formatter is ignored. See

Figure 6-2 for more details.

Bit 1: Payload Loopback (PLB). When set to 1, payload loopback is enabled and the following occurs:

1) Data is transmitted from the TPOSO and TNEGO pins synchronous with RCLKO instead of TCLKT.

2) All the receive side signals continue to operate normally.

3) Data at the TSERI, TDATA, and TSIG pins is ignored.

T1 Mode: Normally, this loopback is only enabled when ESF framing is being performed but can also be enabled in

D4 framing applications. The transceiver loops the 192 bits of payload data (with BPVs corrected) from the receive

section back to the transmit section. The FPS framing pattern, CRC6 calculation, and the FDL bits are not looped

back; they are reinserted by the transceiver.

E1 Mode: The transceiver loops the 248 bits of payload data (with BPVs corrected) from the receive section back

to the transmit section. The transmit section modifies the payload as if it was input at TSERI. The FAS word; Si,

Sa, and E bits; and CRC4 are not looped back; they are reinserted by the transceiver.

Bit 0: Framer Loopback (FLB). When this bit is set to 1, the transceiver loops data from the transmit side back to

the receive side. When FLB is enabled, the following occurs:

1) T1 Mode: An unframed all-ones code is transmitted at TPOSO and TNEGO.

E1 Mode: Normal data is transmitted at TPOSO and TNEGO.

2) Data at RPOSI and RNEGI is ignored.

3) All receive-side signals take on timing synchronous with TCLKT instead of RDCLKI.

Please note that it is not acceptable to have RCLKO connected to TCLKT during this loopback because this

causes an unstable condition.