DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

57 of 344

The MAC circuitry generates a frame status for every frame that is received. This real time status can be read by

SU.RFSB0 to SU.RFSB3. Note the frame status is the “real time” status and hence the value will change as new

frames are received. Hence the real time status reflects the status in time and may not correspond to the current

received frame being processed. This is also true for the transmitted frames.

Frames with errors are usually rejected by the DS33R11. The user has the option of accepting frames by settings

in Receive Frame Rejection Control register (

SU.RFRC). The user can program whether to reject or accept frames

with the following errors:

• MII error asserted during the reception of the frame

• Dribbling bits occurred in the frame

• CRC error occurred

• Length error occurred—the length indicated by the frame length is inconsistent with the number of bytes

received

• Control frame was received. The mode must be full duplex

• Unsupported control frame was received

Note that frames received that are runt frames or frames with collision will automatically be rejected.

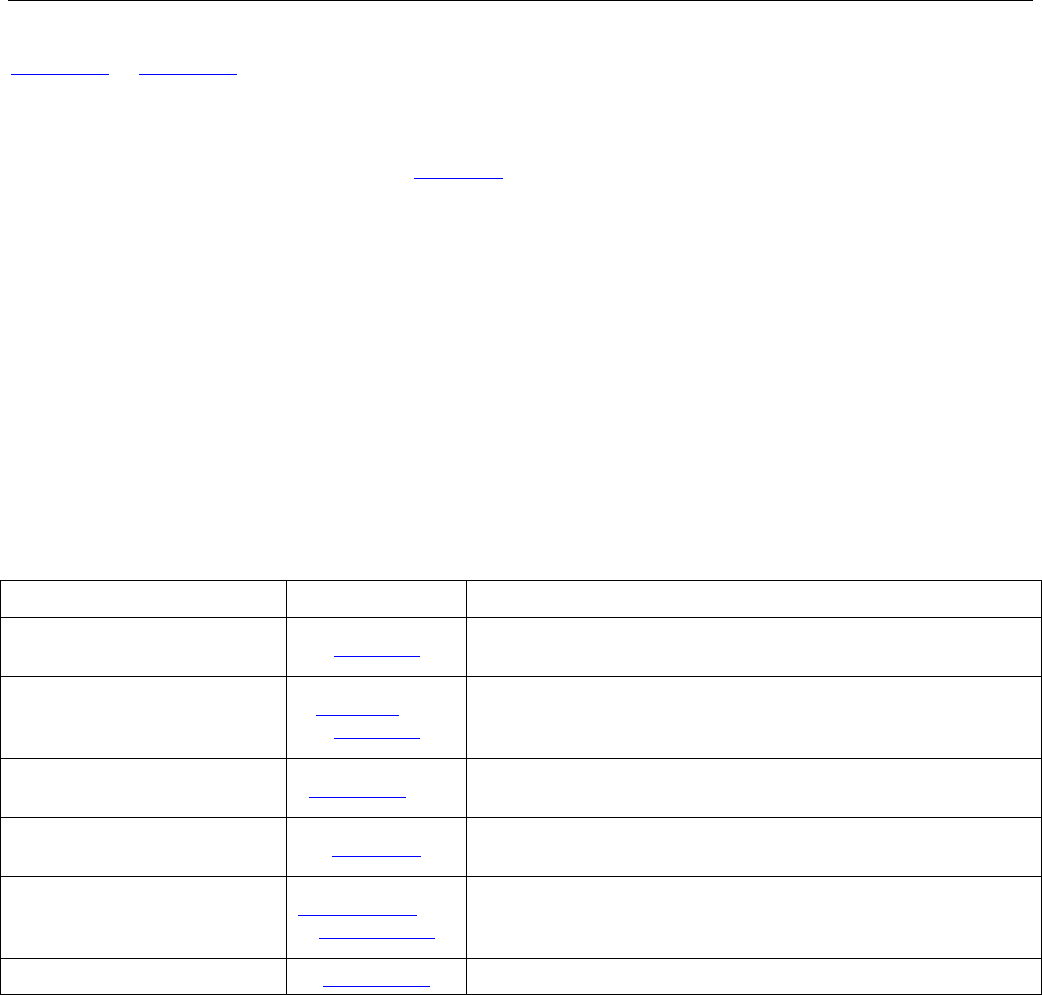

Table 9-5. Registers Related to Setting the Ethernet Port

REGISTER NAME FUNCTION

Transmit Frame Resend

Control

SU.TFRC

This register determines if the current frame is retransmitted

due to various transmit errors.

Transmit Frame Status Low

and Transmit Frame Status

High

SU.TFSL and

SU.TFSH

These two registers provide the real-time status of the

transmit frame. Only apply to the last frame transmitted.

Receive Frame Status Byte 0

to 3

SU.RFSB0 to 3

These registers provide the real-time status for the received

frame. Only apply to the last frame received.

Receive Frame Rejection

Control

SU.RFRC

This register provides settings for reception or rejection of

frame based on errors detected by the MAC.

Receiver Maximum Frame

High and Receiver Maximum

Frame Low

SU.RMFSRH and

SU.RMFSRL

The settings for this register provide the maximum size of

frames to be accepted from the MII/RMII receive interface.

MAC Control SU.MACCR This register provides configuration control for the MAC.