DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

79 of 344

10.7.2 Path Code Violation Count Register (TR.PCVCR)

In T1 mode, the path code violation count register records Ft, Fs, or CRC6 errors in T1 frames. When the receive

side of a framer is set to operate in the T1 ESF framing mode, TR.PCVCR records errors in the CRC6 codewords.

When set to operate in the T1 D4 framing mode, TR.PCVCR counts errors in the Ft framing bit position. Through

the TR.ERCNT.2 bit, a framer can be programmed to also report errors in the Fs framing bit position. The

TR.PCVCR is disabled during receive loss-of-synchronization (RLOS = 1) conditions.

Table 10-7 shows what

errors the TR.PCVCR counts.

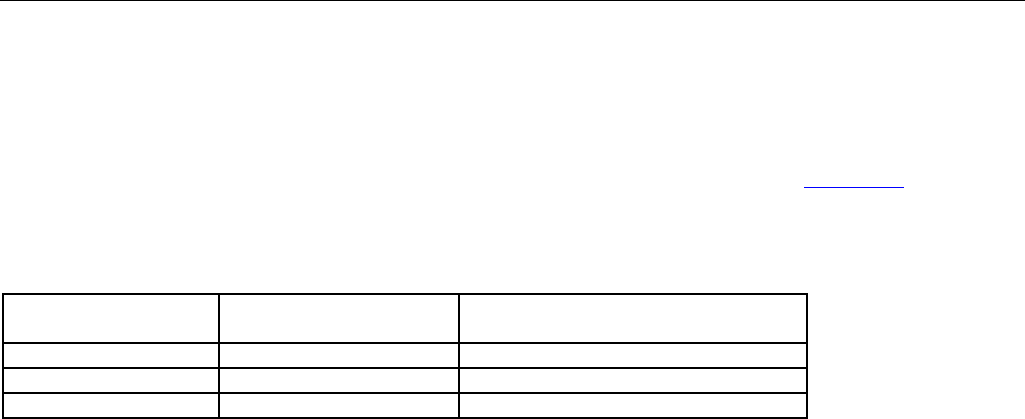

Table 10-7. T1 Path Code Violation Counting Arrangements

FRAMING MODE COUNT Fs ERRORS?

COUNTED

IN THE PCVCRs

D4 No Errors in the Ft pattern

D4 Yes Errors in both the Ft and Fs patterns

ESF Don’t Care Errors in the CRC6 codewords

In E1 mode, the path code violation-count register records CRC4 errors. Since the maximum CRC4 count in a one-

second period is 1000, this counter cannot saturate. The counter is disabled during loss-of-sync at either the FAS

or CRC4 level; it continues to count if loss-of-multiframe sync occurs at the CAS level.

Path code violation-count register 1 (TR.PCVCR1) is the most significant word and TR.PCVCR2 is the least

significant word of a 16-bit counter that records path violations (PVs).