DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

82 of 344

10.9 Signaling Operation

There are two methods to access receive signaling data and provide transmit signaling data, processor-based

(software-based) or hardware-based. Processor-based refers to access through the transmit and receive signaling

registers RS1–RS16 and TS1–TS16. Hardware-based refers to the TSIG and RSIG pins. Both methods can be

used simultaneously.

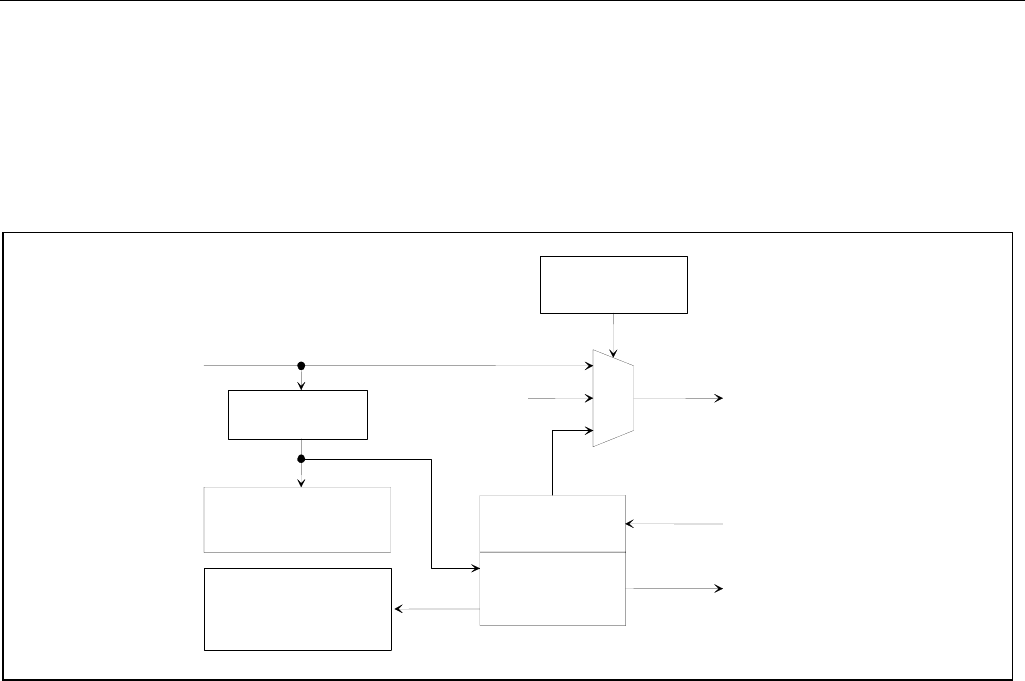

Figure 10-2. Simplified Diagram of Receive Signaling Path

RECEIVE SIGNALING

REGISTERS

CHANGE-OF-STATE

INDICATION

REGISTERS

SIGNALING

BUFFERS

A

LL-ONES

REINSERTION

CONTROL

RSERO

RSYNC

RSIG

T1/E1 DATA STREAM

PER-CHANNEL

CONTROL

SIGNALING

EXTRACTION

10.9.1 Processor-Based Receive Signaling

The robbed-bit signaling (T1) or TS16 CAS signaling (E1) is sampled in the receive data stream and copied into

the receive signaling registers, RS1–RS16. In T1 mode, only RS1–RS12 are used. The signaling information in

these registers is always updated on multiframe boundaries. This function is always enabled.

10.9.1.1 Change-of-State

To avoid constant monitoring of the receive signaling registers, the transceiver can be programmed to alert the

host when any specific channel or channels undergo a change of their signaling state. TR.RSCSE1–TR.RSCSE4

for E1 and TR.RSCSE1–TR.RSCSE3 for T1 are used to select which channels can cause a change-of-state

indication. The change-of-state is indicated in status register 5 (TR.SR1.5). If signaling integration (TR.CCR1.5) is

enabled, then the new signaling state must be constant for three multiframes before a change-of-state is indicated.

The user can enable the INT pin to toggle low upon detection of a change in signaling by setting the TR.IMR1.5 bit.

The signaling integration mode is global and cannot be enabled on a channel-by-channel basis.

The user can identity which channels have undergone a signaling change-of-state by reading the TR.RSINFO1–

TR.RSINFO4 registers. The information from these registers inform the user which TR.RSx register to read for the

new signaling data. All changes are indicated in the TR.RSINFO1–TR.RSINFO4 registers regardless of the

TR.RSCSE1–TR.RSCSE4 registers.