DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

23 of 344

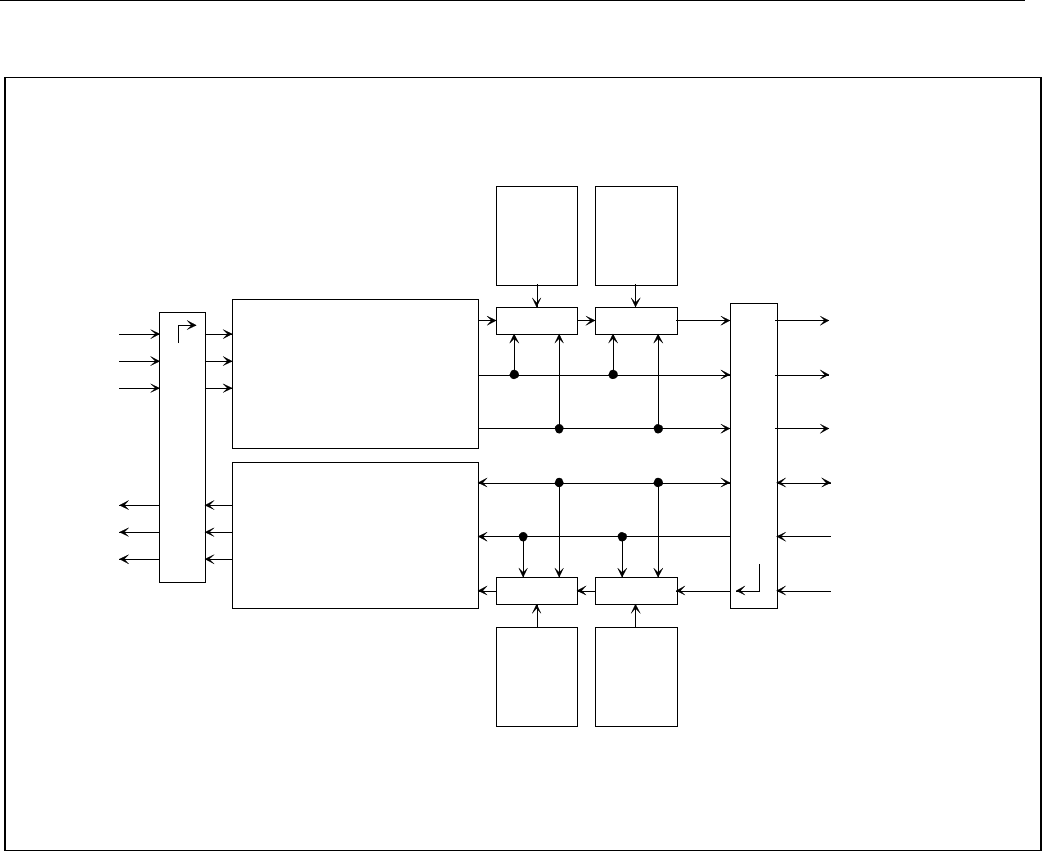

Figure 6-4. Receive and Transmit T1/E1/J1 Framer

RECEIVE

FRAMER

TRANSMIT

FRAMER

DATA

CLOCK

SYNC

SYNC

CLOCK

DATA

FRAMER LOOPBACK

XMIT

HDLC #1

MAPPER

XMIT

HDLC #2

MAPPER

128 Byte

FIFO

128 Byte

FIFO

MAPPER MAPPER

REC

HDLC #1

REC

HDLC #2

128 Byte

FIFO

128 Byte

FIFO

DATA

CLOCK

SYNC

SYNC

CLOCK

DATA

RPOS

RNEG

RCLK

TPOS

TNEG

TCLK

PAYLOAD LOOPBACK

INTERNAL

SIGNALS

FROM

LIU

INTERNAL

SIGNALS

TO

BACKPLANE

INTERFACE