DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

89 of 344

10.12.2 Transmit Elastic Store

See the TR.IOCR1 and TR.IOCR2 registers for information about clock and I/O configurations. The operation of

the transmit elastic store is very similar to the receive side. If the transmit-side elastic store is enabled, a 1.544MHz

or 2.048MHz clock can be applied to the TSYSCLK input. Controlled slips in the transmit elastic store are reported

in the TR.SR5.3 bit, and the direction of the slip is reported in the TR.SR5.4 and TR.SR5.5 bits. If hardware

signaling insertion is not enabled, TR.CCR3.7 should be set = 1.

10.12.2.1 T1 Mode

If the user selects to apply a 2.048MHz clock to the TSYSCLK pin, then the data input at TSERI is ignored every

fourth channel. Therefore channels 1, 5, 9, 13, 17, 21, 25, and 29 (time slots 0, 4, 8, 12, 16, 20, 24, and 28) are

ignored. The user can supply frame or multiframe sync pulse to the TSSYNC input. Also, in 2.048MHz

applications, the TCHBLK output is forced high during the channels ignored by the framer.

10.12.2.2 E1 Mode

A 1.544MHz or 2.048MHz clock can be applied to the TSYSCLK input. The user must supply a frame sync pulse or

a multiframe sync pulse to the TSSYNC input.

10.12.3 Elastic Stores Initialization

There are two elastic store initializations that can be used to improve performance in certain applications, elastic

store reset and elastic store align. Both of these involve the manipulation of the elastic store’s read and write

pointers and are useful primarily in synchronous applications (RSYSCLK/TSYSCLK are locked to RCLKO/TCLKT,

respectively) (

Table 10-11).

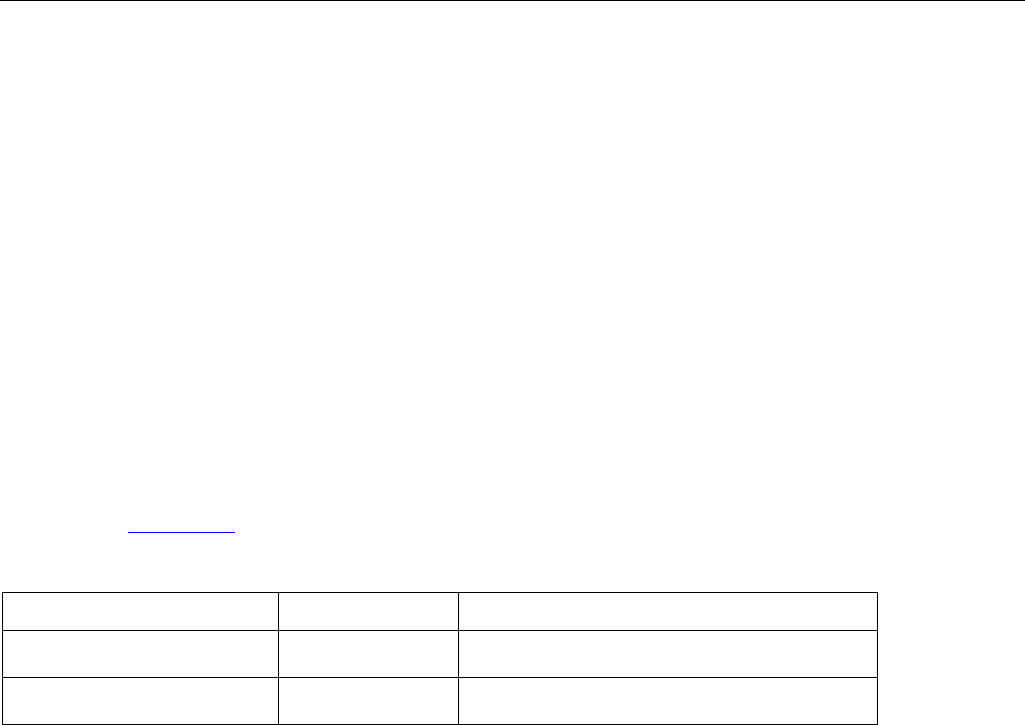

Table 10-11. Elastic Store Delay After Initialization

INITIALIZATION REGISTER BIT DELAY

Receive Elastic Store Reset

Transmit Elastic Store Reset

TR.ESCR.2

TR.ESCR.6

8 Clocks < Delay < 1 Frame

1 Frame < Delay < 2 Frames

Receive Elastic Store Align

Transmit Elastic Store Align

TR.ESCR.3

TR.ESCR.7

½ Frame < Delay < 1 ½ Frames

½ Frame < Delay < 1 ½ Frames

10.12.4 Minimum Delay Mode

Elastic store minimum delay mode can be used when the elastic store’s system clock is locked to its network clock

(i.e., RCLKO locked to RSYSCLK for the receive side and TCLKT locked to TSYSCLK for the transmit side).

TR.ESCR.5 and TR.ESCR.1 enable the transmit and receive elastic store minimum delay modes. When enabled,

the elastic stores are forced to a maximum depth of 32 bits instead of the normal two-frame depth. This feature is

useful primarily in applications that interface to a 2.048MHz bus. Certain restrictions apply when minimum delay

mode is used. In addition to the restriction mentioned above, RSYNC must be configured as an output when the

receive elastic store is in minimum delay mode; TSYNC must be configured as an output when transmit minimum

delay mode is enabled. In a typical application, RSYSCLK and TSYSCLK are locked to RCLKO, and RSYNC

(frame output mode) is connected to TSSYNC (frame input mode). All of the slip contention logic in the framer is

disabled (since slips cannot occur). On power-up, after the RSYSCLK and TSYSCLK signals have locked to their

respective network clock signals, the elastic store reset bits (TR.ESCR.2 and TR.ESCR.6) should be toggled from

a 0 to a 1 to ensure proper operation.