DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

67 of 344

Bit reordering changes the bit order of each byte. If bit reordering is disabled, the incoming 8-bit data stream

DT[1:8] with DT[1] being the MSB and DT[8] being the LSB is output to the Receive FIFO with the MSB in RFD[7]

(or 15, 23, or 31) and the LSB in RFD[0] (or 8, 16, or 24) of the receive FIFO data RFD[7:0] (or 15:8, 23:16, or

31:24). If bit reordering is enabled, the incoming 8-bit data stream DT[1:8] is output to the Receive FIFO with the

MSB in RFD[0] and the LSB in RFD[7] of the receive FIFO data RFD[7:0]. DT[1] is the first bit received from the

incoming data stream.

Once all of the packet processing has been completed, The 8-bit parallel data stream is demultiplexed into a 32-bit

parallel data stream. The Receive FIFO data is passed on to the Receive FIFO with packet start, packet end,

packet abort, and modulus indications. At a packet end, the 32-bit word may contain 1, 2, 3, or 4 bytes of data

depending on the number of bytes in the packet. The modulus indications indicate the number of bytes in the last

data word of the packet.

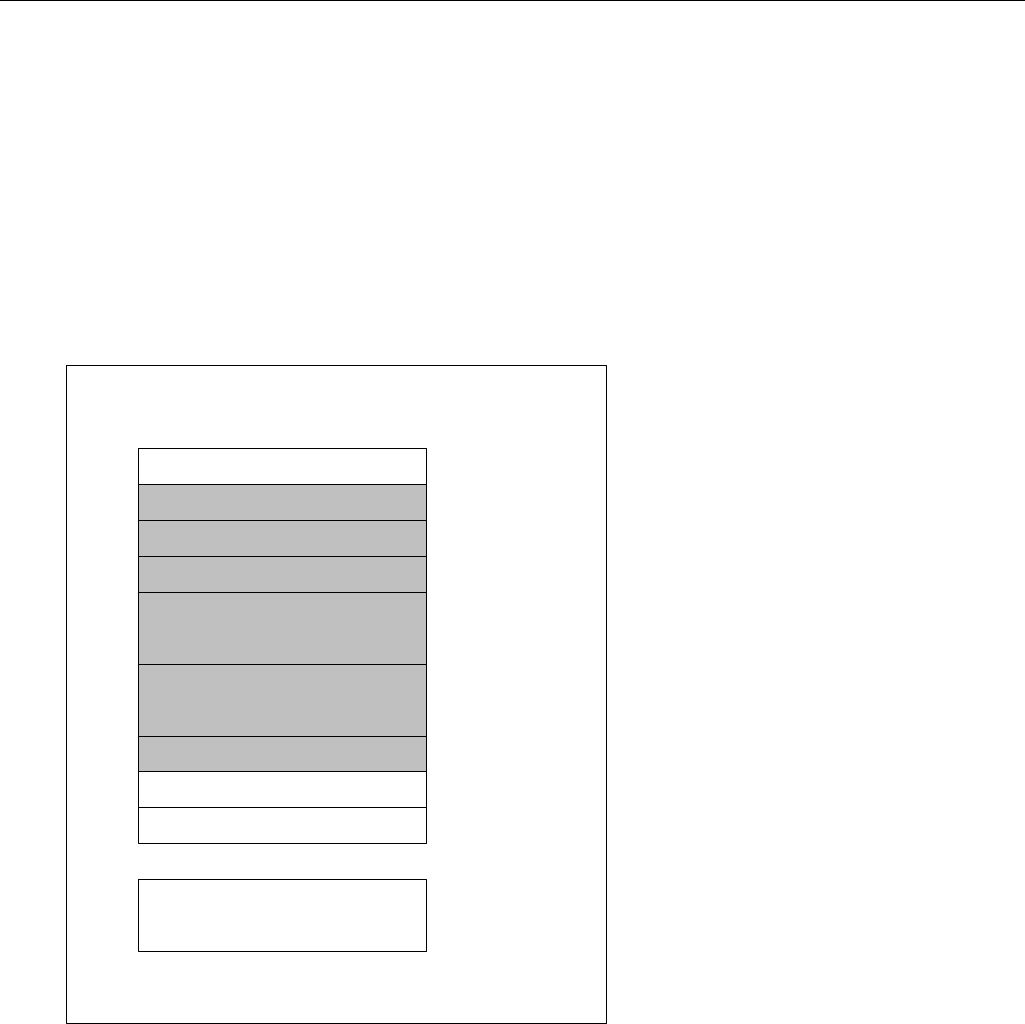

Figure 9-11. HDLC Encapsulation of MAC Frame

Flag(0x7E)

Destination Adrs(DA)

Source Adrs(SA)

Length/Type

Number of Bytes

1

6

6

2

MAC Client Data

46-1500

PAD

FCS for MAC

4

FCS for HDLC

Flag(0x7E)

0 / 2 / 4

MSB LSB