DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

118 of 344

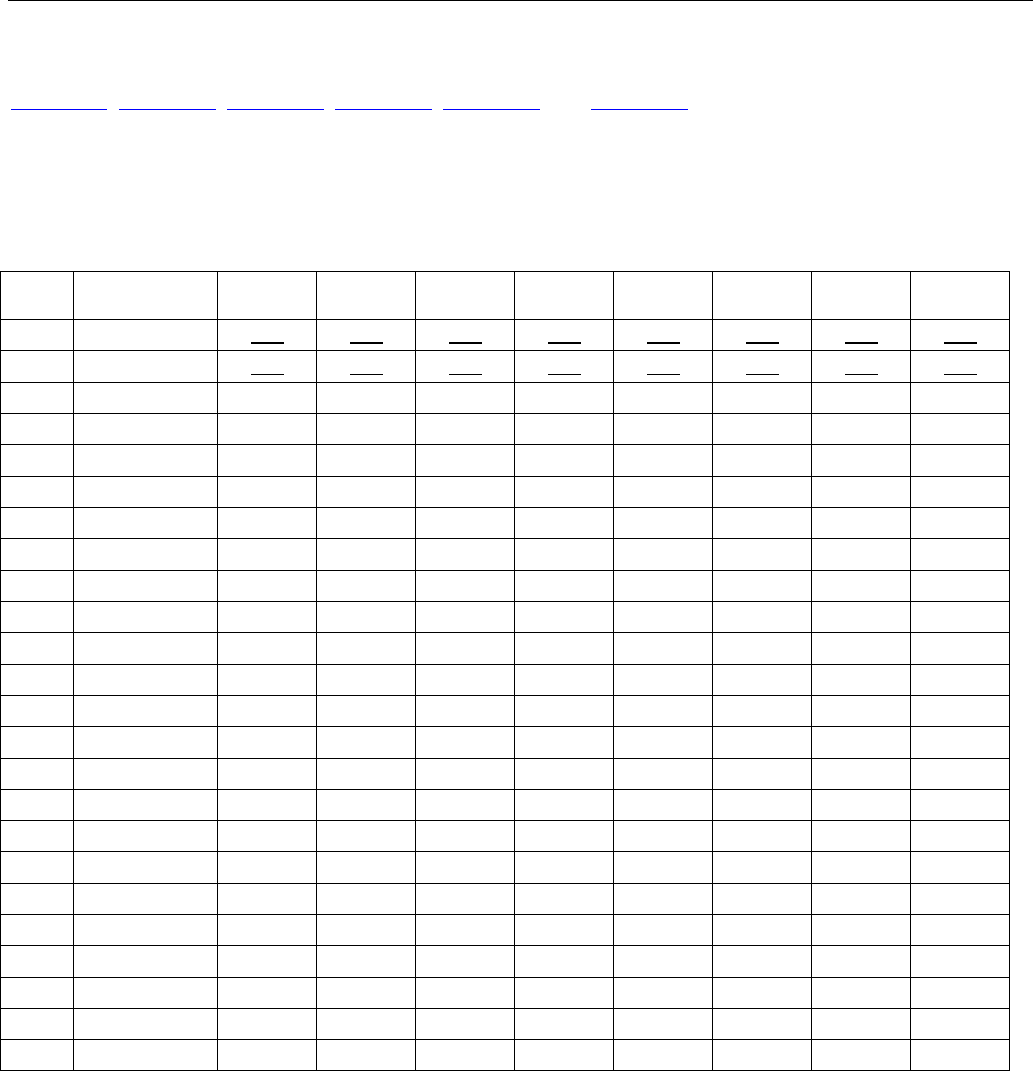

11.1 Register Bit Maps

Table 11-2, Table 11-3, Table 11-4, Table 11-5, Table 11-6, and Table 11-7 contain the registers of the DS33R11.

Bits that are reserved are noted with a single dash “-“. All registers not listed are reserved and should be initialized

with a value of 00h for proper operation, unless otherwise noted.

11.1.1 Global Ethernet Mapper Register Bit Map

Table 11-2. Global Ethernet Mapper Register Bit Map

A

DDR

Name

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

00h

GL.IDRL

ID07 ID06 ID05 ID04 ID03 ID02 ID01 ID00

01h

GL.IDRH

ID15 ID14 ID13 ID12 ID11 ID10 ID09 ID08

02h

GL.CR1

- - - - - REF_CLKO INTM RST

03h

GL.BLR

- - - - - - - GL.BLC1

04h

GL.RTCAL

- - - RLCALS1 - - - TLCALS1

05h

GL.SRCALS

- - - - - - REFCLKS SYSCLS

06h

GL.LIE

- - - LIN1TIE - - - LIN1RIE

07h

GL.LIS

- - - LIN1TIS - - - LIN1RIS

08h

GL.SIE

- - - - - - - SUB1IE

09h

GL.SIS

- - - - - - - SUB1IS

0Ah

GL.TRQIE

- - - TQ1IE - - - RQ1IE

0Bh

GL.TRQIS

- - - TQ1IS - - - RQ1IS

0Ch

GL.BIE

- - - - - - - BIE

0Dh

GL.BIS

- - - - - - - BIS

0Eh

GL.CON1

- - - - - - - LINE0

0Fh

Reserved

- - - - - - - -

10h

Reserved

- - - - - - - -

11h

Reserved

- - - - - - - -

12h

GL.C1QPR

- - - - C1MRPR C1HWPR C1MHPR C1HRPR

13h

Reserved

- - - - - - - -

14h

Reserved

- - - - - - - -

15h

Reserved

- - - - - - - -

20h

GL.BISTEN

- - - - - - - BISTE

21h

GL.BISTPF

- - - - - - BISTDN BISTPF

Note: 22h–3Fh are reserved.