DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

69 of 344

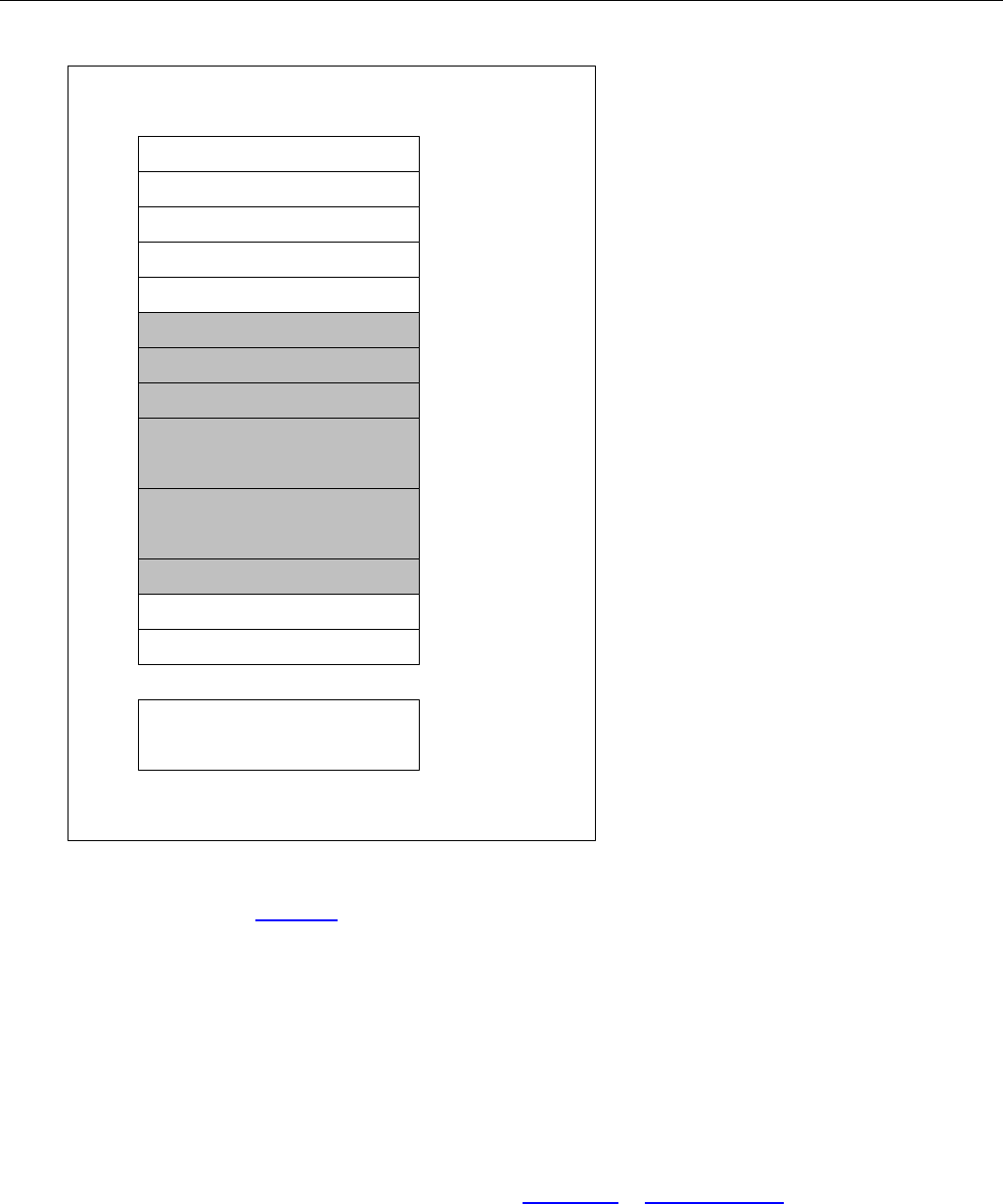

Figure 9-13. X.86 Encapsulation of the MAC frame

Flag(0x7E)

Address(0x04)

Control(0x03)

1st Octect of SAPI(0xfe)

2nd Octect of SAPI(0x01)

Destination Adrs(DA)

Source Adrs(SA)

Length/Type

Number of Bytes

1

1

1

1

1

6

6

2

MAC Client Data

46-1500

PAD

FCS for MAC

4

FCS for LAPS

Flag(0x7E)

4

MSB LSB

The DS33R11 will encode the MAC Frame with the LAPS encapsulation on a complete serial stream if configured

for X.86 mode in the register

LI.TX86E. The DS33R11 provides the following functions:

• Control Registers for Address, Control, SAPIH, SAPIL.

• 32 bit FCS enabled.

• Programmable X

43

+1 scrambling.

The sequence of processing performed by the receiver is as follows:

• Programmable octets X

43

+1 descrambling.

• Detect the Start Flag (7E).

• Remove Rate adaptation octets 7d, dd.

• Perform transparency-processing 7d, 5e is converted to 7e and 7d, 5d is converted to 7d.

• Check for a valid Address, Control and SAPI fields (

LI.TRX86A to LI.TRX86SAPIL).

• Perform FCS checking.

• Detect the closing flag.