DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

340 of 344

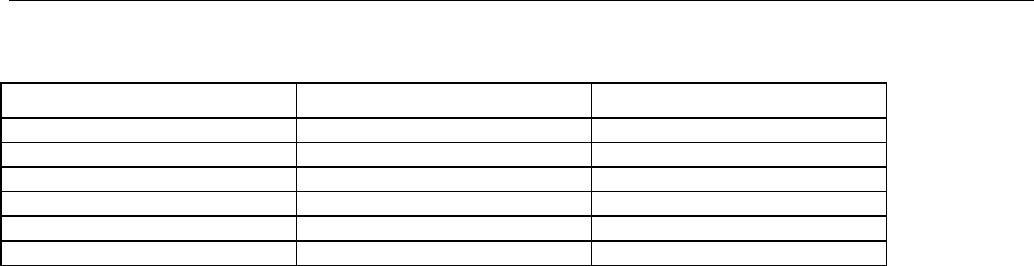

Table 14-1. Instruction Codes for IEEE 1149.1 Architecture

INSTRUCTION SELECTED REGISTER INSTRUCTION CODES

SAMPLE:PRELOAD Boundary Scan 010

BYPASS Bypass 111

EXTEST Boundary Scan 000

CLAMP Bypass 011

HIGHZ Bypass 100

IDCODE Device Identification 001

SAMPLE:PRELOAD

This is a mandatory instruction for the IEEE 1149.1 specification. This instruction supports two functions. The

digital I/Os of the device can be sampled at the boundary scan register without interfering with the normal

operation of the device by using the Capture-DR state. SAMPLE:PRELOAD also allows the device to shift data

into the boundary scan register via JTDI using the Shift-DR state.

BYPASS

When the BYPASS instruction is latched into the parallel instruction register, JTDI connects to JTDO through the

one-bit bypass test register. This allows data to pass from JTDI to JTDO not affecting the device’s normal

operation.

EXTEST

This allows testing of all interconnections to the device. When the EXTEST instruction is latched in the instruction

register, the following actions occur. Once enabled via the Update-IR state, the parallel outputs of all digital output

pins are driven. The boundary scan register is connected between JTDI and JTDO. The Capture-DR will sample

all digital inputs into the boundary scan register.

CLAMP

All digital outputs of the device will output data from the boundary scan parallel output while connecting the bypass

register between JTDI and JTDO. The outputs will not change during the CLAMP instruction.

HIGHZ

All digital outputs of the device are placed in a high-impedance state. The BYPASS register is connected between

JTDI and JTDO.

IDCODE

When the IDCODE instruction is latched into the parallel instruction register, the identification test register is

selected. The device identification code is loaded into the identification register on the rising edge of JTCLK

following entry into the Capture-DR state. Shift-DR can be used to shift the identification code out serially via

JTDO. During Test-Logic-Reset, the identification code is forced into the instruction register’s parallel output. The

ID code will always have a ‘1’ in the LSB position. The next 11 bits identify the manufacturer’s JEDEC number and

number of continuation bytes followed by 16 bits for the device and 4 bits for the version.