DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

292 of 344

Register Name:

TR.BC1

Register Description:

BERT Control Register 1

Register Address:

E0h

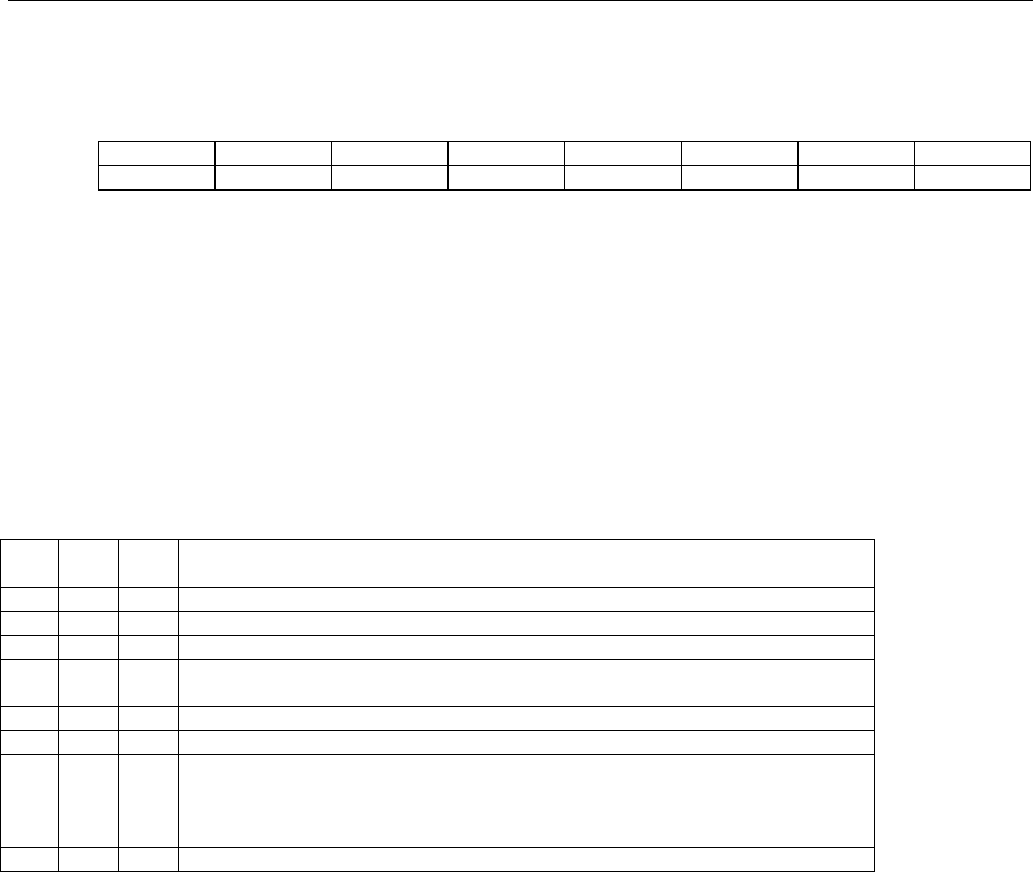

Bit # 7 6 5 4 3 2 1 0

Name TC TINV RINV PS2 PS1 PS0 LC RESYNC

Default 0 0 0 0 0 0 0 0

Bit 7: Transmit Pattern Load (TC). A low-to-high transition loads the pattern generator with the pattern that is to

be generated. This bit should be toggled from low to high whenever the host wishes to load a new pattern. Must be

cleared and set again for subsequent loads.

Bit 6: Transmit Invert-Data Enable (TINV)

0 = do not invert the outgoing data stream

1 = invert the outgoing data stream

Bit 5: Receive Invert-Data Enable (RINV)

0 = do not invert the incoming data stream

1 = invert the incoming data stream

Bits 2 – 4: Pattern Select Bits (PS0 to PS2)

PS

2

PS1 PS0 Pattern Definition

0 0 0 Pseudorandom 2E7 - 1

0 0 1 Pseudorandom 2E11 - 1

0 1 0 Pseudorandom 2E15 - 1

0 1 1

Pseudorandom pattern QRSS. A 2

20

- 1 pattern with 14 consecutive zero

restrictions.

1 0 0 Repetitive pattern

1 0 1 Alternating word pattern

1 1 0

Modified 55 octet (Daly) pattern. The Daly pattern is a repeating 55 octet

pattern that is byte-aligned into the active DS0 time slots. The pattern is

defined in an ATIS (Alliance for Telecommunications Industry Solutions)

Committee T1 Technical Report Number 25 (November 1993).

1 1 1 Pseudorandom 2E9 – 1

Bit 1: Load Bit and Error Counters (LC). A low-to-high transition latches the current bit and error counts into

registers TR.BBC1/ TR.BBC2/ TR.BBC3/ TR.BBC4 and TR.BEC1/ TR.BEC2/ TR.BEC3 and clears the internal

count. This bit should be toggled from low to high whenever the host wishes to begin a new acquisition period.

Must be cleared and set again for subsequent loads.

Bit 0: Force Resynchronization (RESYNC). A low-to-high transition forces the receive BERT synchronizer to

resynchronize to the incoming data stream. This bit should be toggled from low to high whenever the host wishes

to acquire synchronization on a new pattern. Must be cleared and set again for a subsequent resynchronization.