Rev. 1.00, 05/04, page 73 of 544

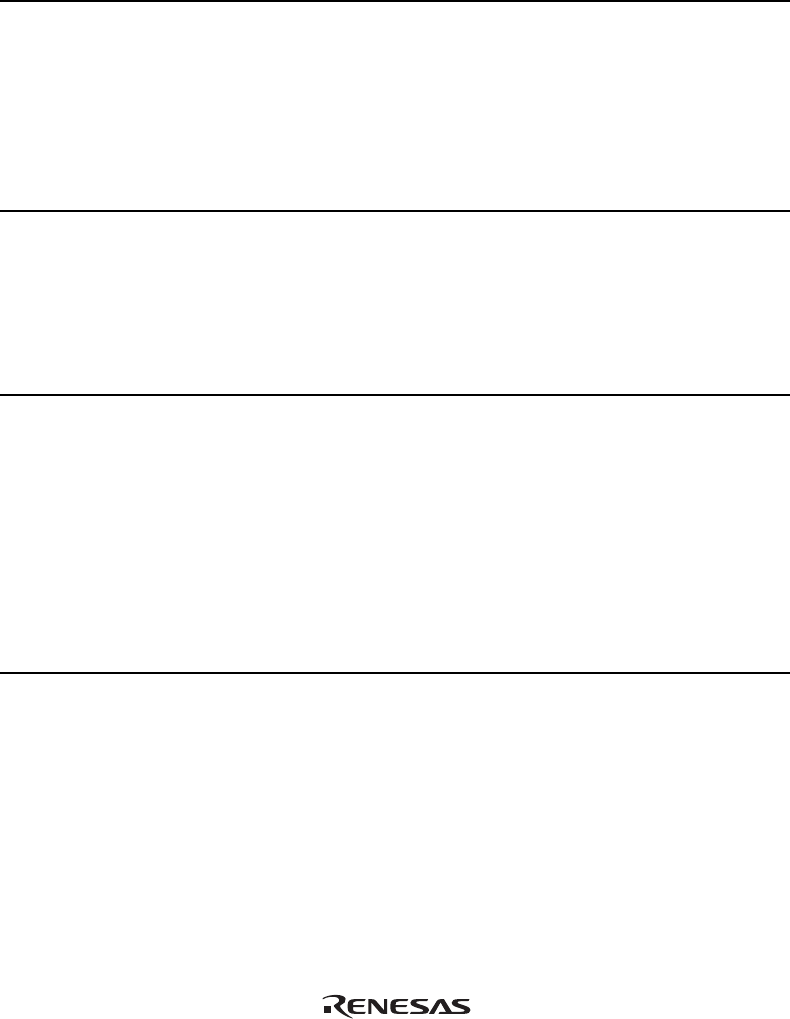

5.3.5 IRQ Enable Register (IER)

IER controls the enabling and disabling of interrupt requests IRQ7 to IRQ0.

Bit Bit Name

Initial

Value R/W Description

7

6

5

4

3

2

1

0

IRQ7E

IRQ6E

IRQ5E

IRQ4E

IRQ3E

IRQ2E

IRQ1E

IRQ0E

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

IRQn Enable (n = 7 to 0)

The IRQn interrupt request is enabled when this bit is

1.

5.3.6 IRQ Status Register (ISR)

The ISR register is a flag register that indicates the status of IRQ7 to IRQ0 interrupt requests.

Bit Bit Name

Initial

Value

R/W Description

7

6

5

4

3

2

1

0

IRQ7F

IRQ6F

IRQ5F

IRQ4F

IRQ3F

IRQ2F

IRQ1F

IRQ0F

0

0

0

0

0

0

0

0

R/(W)*

R/(W)*

R/(W)*

R/(W)*

R/(W)*

R/(W)*

R/(W)*

R/(W)*

[Setting condition]

When the interrupt source selected by the ISCR

registers occurs

[Clearing conditions]

When reading IRQnF flag when IRQnF = 1, then

writing 0 to IRQnF flag

When interrupt exception handling is executed when

low-level detection is set and IRQn input is high

(n = 7 to 0)

When IRQn interrupt exception handling is executed

when falling-edge, rising-edge, or both-edge detection

is set

Note: * Only 0 can be written, for flag clearing.

5.3.7 Keyboard Matrix Interrupt Mask Registers (KMIMRA, KMIMR)

Wake-Up Event Interrupt Mask Register (WUEMRB)

The KMIMRA, KMIMR, and WUEMRB registers enable or disable key-sensing interrupt inputs

(KIN15 to KIN0), and wake-up event interrupt inputs (WUE7 to WUE0).