Rev. 1.00, 05/04, page 359 of 544

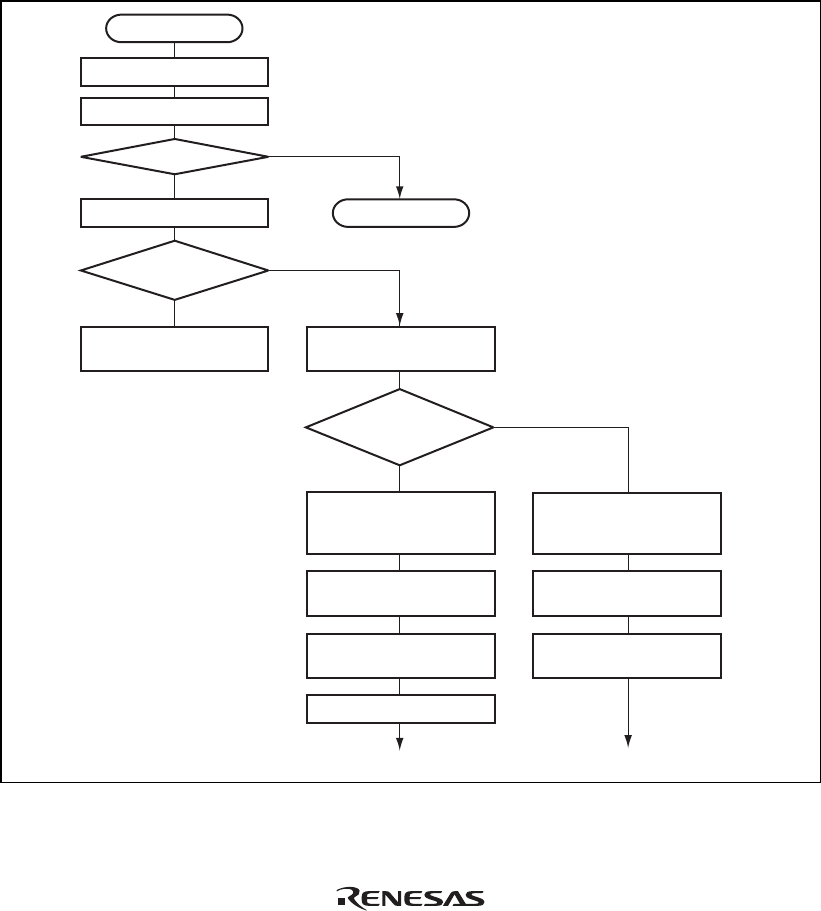

14.4.3 Receive Abort

This LSI (system side) can forcibly abort transmission from the device connected to it (keyboard

side) in the event of a protocol error, etc. In this case, the system holds the clock low. During

reception, the keyboard also outputs a clock for synchronization, and the clock is monitored when

the keyboard output clock is high. If the clock is low at this time, the keyboard judges that there is

an abort request from the system, and data transmission from the keyboard is aborted. Thus the

system can abort reception by holding the clock low for a certain period. A sample receive abort

processing flowchart is shown in figure 14.7, and the receive abort timing in figure 14.8.

Read KBCRL

KBF = 0?

RXCR3 to RXCR0 ≥

B'1001?

Disable receive abort

requests

Yes

Start

Receive state

Read KBCRH

Processing 1

KCLKO = 0

(receive abort request)

Retransmit

command transmission

(data)?

KBE = 0

(disable KBBR reception

and clear receive counter)

Set start bit

(KDO = 0)

Clear I/O inhibit

(KCLKO = 1)

Transmit data

To transmit operation

KBE = 0

(disable KBBR reception

and clear receive counter)

KBE = 1

(enable KB operation)

Clear I/O inhibit

(KCLKO = 1)

To receive operation

[1] Read KBCRL, and if KBF = 1,

perform processing 1.

[2] Read KBCRH, and if the value of

bits RXCR3 to RXCR0 is less

than B'1001, write 0 in KCLKO to

abort reception.

If the value of bits RXCR3 to

RXCR0 is B'1001 or greater, wait

until stop bit reception is

completed, then perform receive

data processing, and proceed to

the next operation.

[3] If the value of bits RXCR3 to

RXCR0 is B'1001 or greater, the

parity bit is being received. With

the PS2 interface, a receive abort

request following parity bit

reception is disabled. Wait until

stop bit reception is completed,

perform receive data processing

and clear the KBF flag, then

proceed to the next operation.

Yes

No

No

No

Yes

[1]

[2][3]

Figure 14.7 Sample Receive Abort Processing Flowchart (1)