Rev. 1.00, 05/04, page 150 of 544

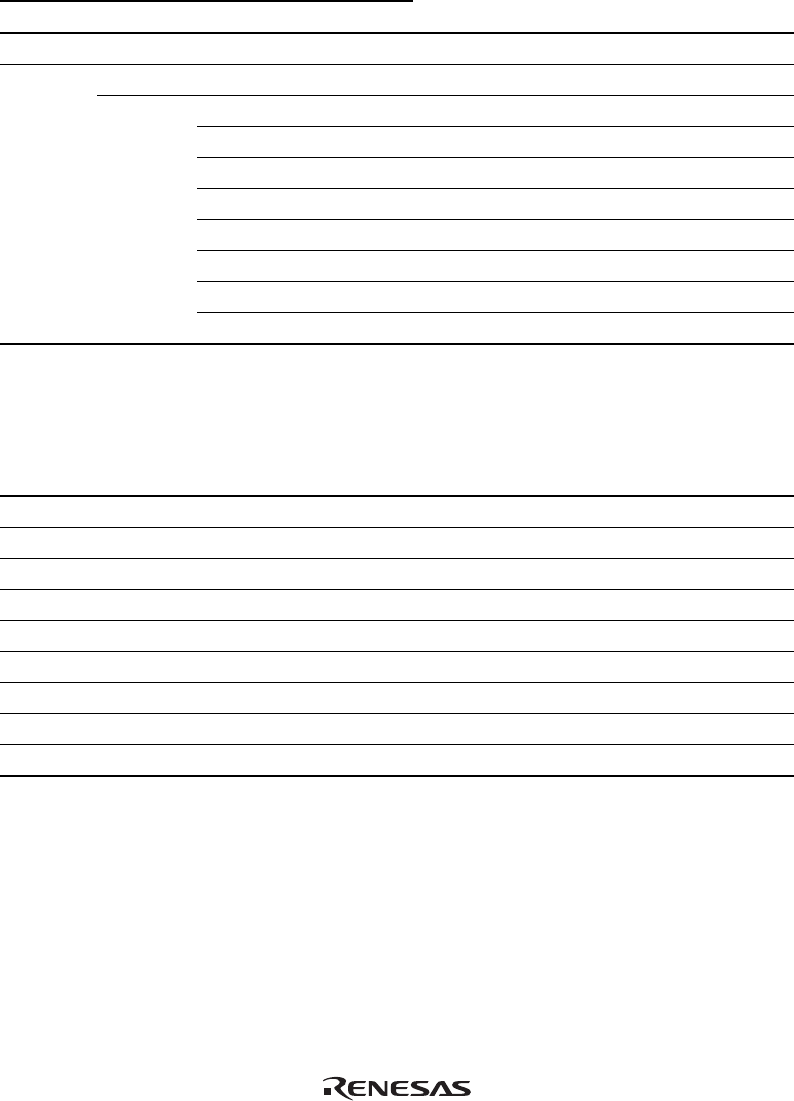

Table 8.2 Internal Clock Selection

PWSL PCSR

PWCKE PWCKS PWCKC PWCKB PWCKA Description

0 — — — — Clock input is disabled (Initial value)

1 0 — — — φ (system clock) is selected

1 0 0 0 φ/2 is selected

0 0 1 φ/4 is selected

0 1 0 φ/8 is selected

0 1 1 φ/16 is selected

1 0 0 φ/256 is selected*

1 0 1 φ/512 is selected*

1 1 0 φ/1024 is selected*

1 1 1 φ/4096 is selected*

Note: * The program development tool (emulator) does not support this function.

Table 8.3 Resolution, PWM Conversion Period, and Carrier Frequency when φ = 10 MHz

Internal Clock

Frequency Resolution

PWM

Conversion Period Carrier Frequency

φ 100 ns 25.6 µs 625 kHz

φ/2 200 ns 51.2 µs 312.5 kHz

φ/4 400 ns 102 µs 156.3 kHz

φ/8 800 ns 205 µs 78.1 kHz

φ/16 1.6 µs 410 µs 39.1 kHz

φ/256* 25.6 µs 6.55 ms 2.4 kHz

φ/512* 51.2 µs 13.1 ms 1.2 kHz

φ/1024* 102 µs 26.2 ms 610 kHz

φ/4096* 410 µs 105 ms 152 kHz

Note: * The program development tool (emulator) does not support this function.