Rev. 1.00, 05/04, page 443 of 544

7. Boot mode can be cleared by a reset. Cancel the reset*

2

after driving the reset pin low, waiting

at least 20 states, and then setting the mode pins. Boot mode is also cleared when a WDT

overflow occurs.

8. Do not change the mode pin input levels in boot mode.

9. All interrupts are disabled during programming or erasing of the flash memory.

Notes: 1. Some parts of this area are reserved only for boot mode and therefore should not be

used for any other purpose.

2. After reset is cancelled, mode pin input settings must satisfy the mode programming

setup time (t

MDS

= 4 states).

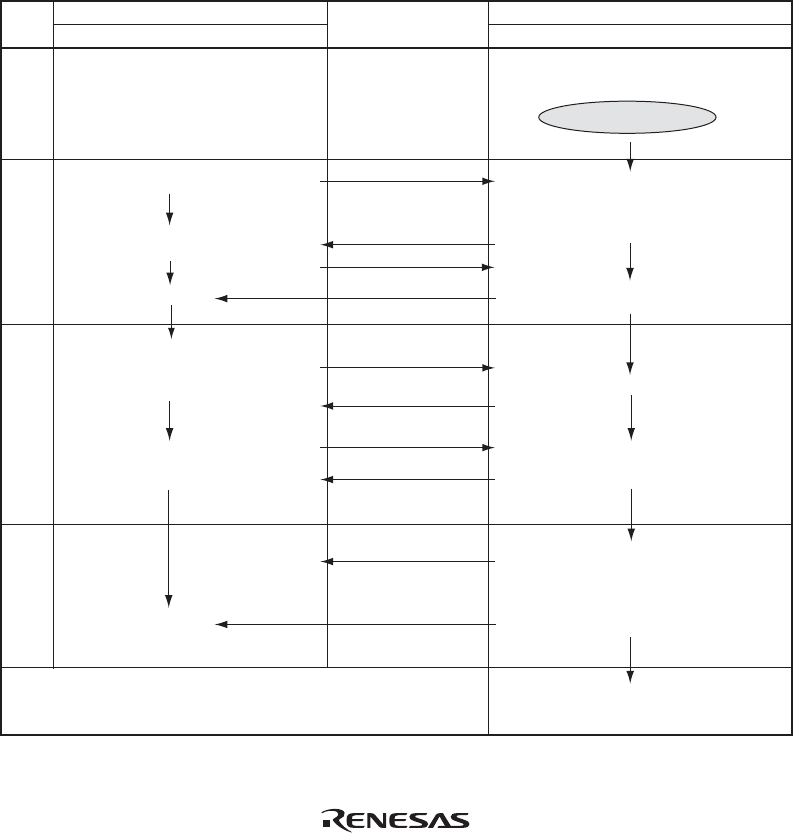

Table 18.5 Boot Mode Operation

Communications Contents

Processing Contents

Host Operation

LSI Operation

Processing Contents

Continuously transmits data H'00

at specified bit rate.

Branches to boot program at reset-start.

Boot program start

Branches to programming control program

transferred to on-chip RAM and starts

execution.

H'00, H'00

. . .

H'00

H'00

H'55

Transmits data H'55 when data H'00

is received error-free.

Boot program

erase error

H'FF

H'AA

Receives data H'AA.

Receives data H'AA.

H'AA

Echobacks the 2-byte data received to host.

Echobacks received data to host and also

transfers it to RAM (repeated for N times).

High-order byte and

low-order byte

Echoback

Echoback

H'XX

Transmits number of bytes (N) of

programming control program to be

transferred as 2-byte data (low-order byte

following high-order byte).

Transmits 1-byte of programming control

program (repeated for N times).

ItemBoot mode start

• Measures low-level period of receive data H'00.

• Calculates bit rate and sets it in BRR of SCI_1.

• Transmits data H'00 to host as adjustment end

indication.

Bit rate adjustment

Checks flash memory data, erases all flash

memory blocks in case of written data

existing, and transmits data H'AA to host.

(If erase could not be done, transmits data

H'FF to host and aborts operation.)

Flash memory erase

Transfer of programming

control program

After receiving data H'55, transmits data

H'AA to host.