Rev. 1.00, 05/04, page 264 of 544

12.6 Operation in Clocked Synchronous Mode

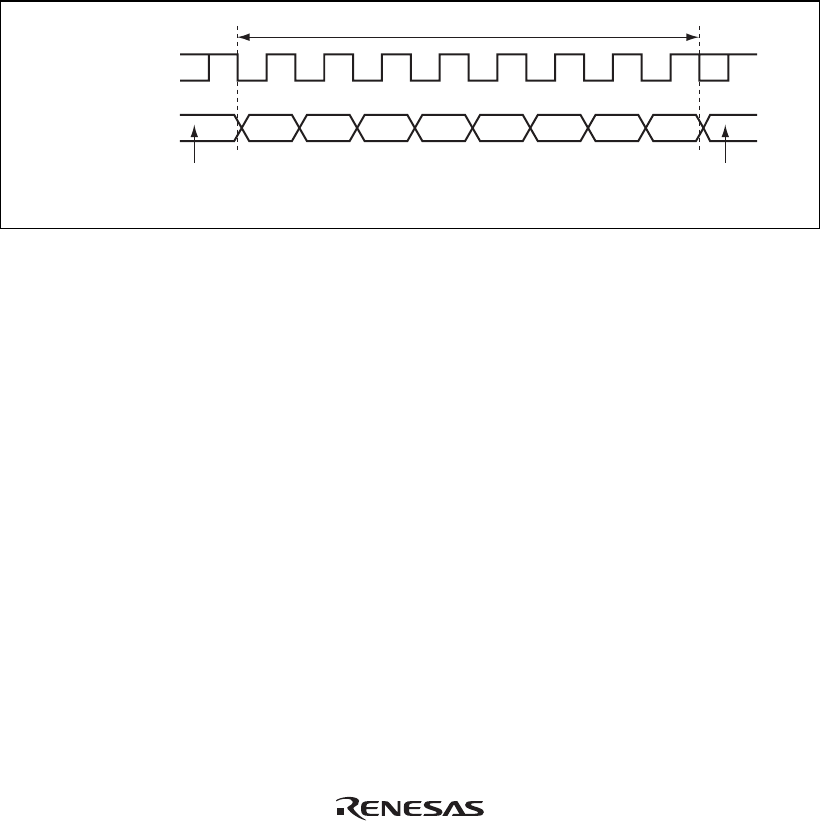

Figure 12.14 shows the general format for clocked synchronous communication. In clocked

synchronous mode, data is transmitted or received in synchronization with clock pulses. One

character in transfer data consists of 8-bit data. In data transmission, the SCI outputs data from one

falling edge of the synchronization clock to the next. In data reception, the SCI receives data in

synchronization with the rising edge of the synchronization clock. After 8-bit data is output, the

transmission line holds the MSB state. In clocked synchronous mode, no parity or multiprocessor

bit is added. Inside the SCI, the transmitter and receiver are independent units, enabling full-

duplex communication by use of a common clock. Both the transmitter and the receiver also have

a double-buffered structure, so that the next transmit data can be written during transmission or the

previous receive data can be read during reception, enabling continuous data transfer.

Don’t

care

Don’t

care

One unit of transfer data (character or frame)

Bit 0

Serial data

Synchronization

clock

Bit 1

Bit 3

Bit 4

Bit 5

LSB

MSB

Bit 2

Bit 6 Bit 7

*

*

Note: * High except in continuous transfer/reception

Figure 12.14 Data Format in Clocked Synchronous Communication (LSB-First)

12.6.1 Clock

Either an internal clock generated by the on-chip baud rate generator or an external

synchronization clock input at the SCK pin can be selected, according to the setting of the CKE1

and CKE0 bits in SCR. When the SCI is operated on an internal clock, the synchronization clock

is output from the SCK pin. Eight synchronization clock pulses are output in the transfer of one

character, and when no transfer is performed the clock is fixed high.