Rev. 1.00, 05/04, page 170 of 544

9.5 Operation Timing

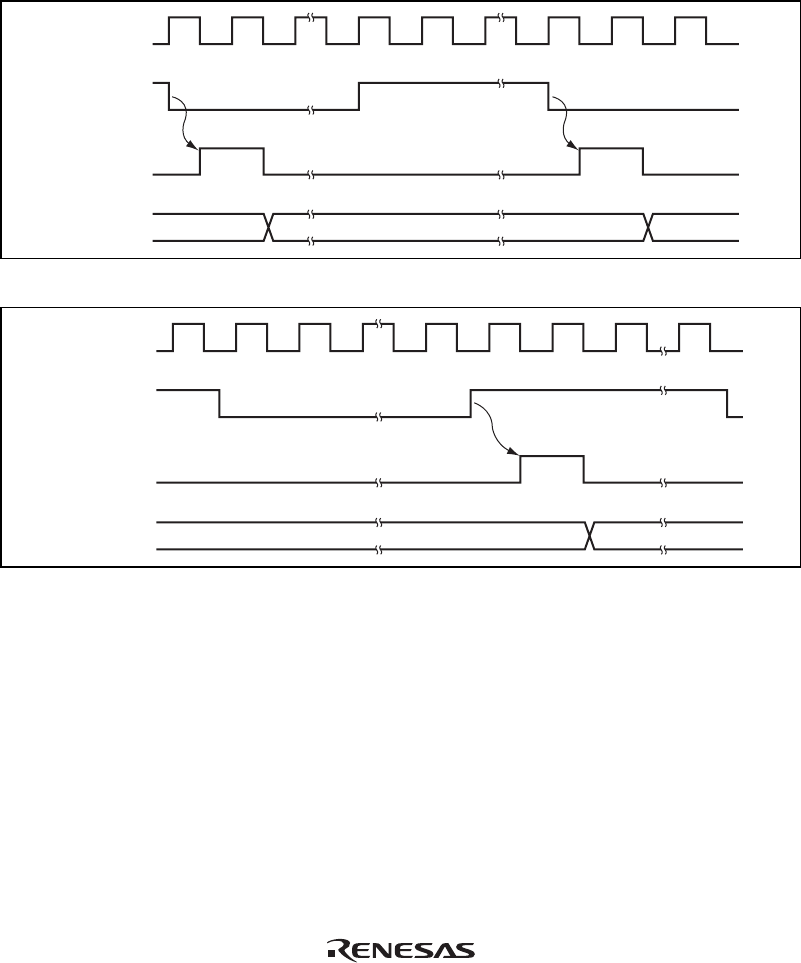

9.5.1 FRC Increment Timing

Figure 9.3 shows the FRC increment timing with an internal clock source. Figure 9.4 shows the

increment timing with an external clock source. The pulse width of the external clock signal must

be at least 1.5 system clocks (φ). The counter will not increment correctly if the pulse width is

shorter than 1.5 system clocks (φ).

φ

Internal clock

FRC input

clock

FRC N – 1 N + 1N

Figure 9.3 Increment Timing with Internal Clock Source

φ

External clock

input pin

FRC input

clock

FRC N + 1N

Figure 9.4 Increment Timing with External Clock Source