Rev. 1.00, 05/04, page 265 of 544

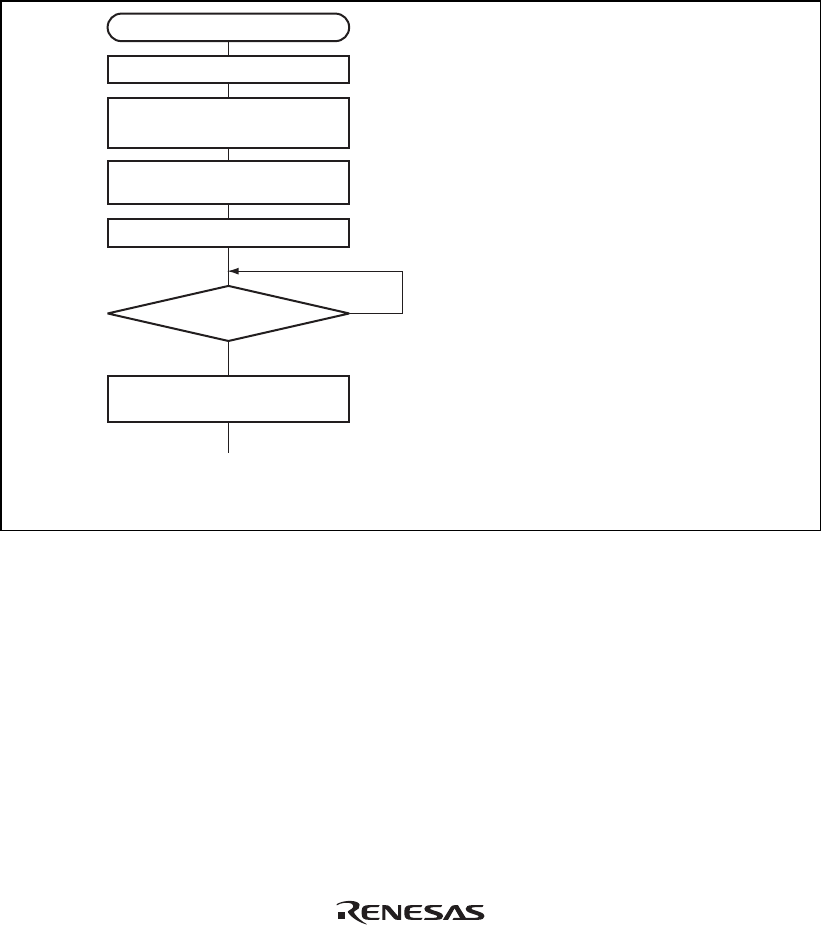

12.6.2 SCI Initialization (Clocked Synchronous Mode)

Before transmitting and receiving data, you should first clear the TE and RE bits in SCR to 0, then

initialize the SCI as described in a sample flowchart in figure 12.15. When the operating mode,

transfer format, etc., is changed, the TE and RE bits must be cleared to 0 before making the

change using the following procedure. When the TE bit is cleared to 0, the TDRE flag in SSR is

set to 1. However, clearing the RE bit to 0 does not initialize the RDRF, PER, FER, and ORER

flags in SSR, or RDR.

Wait

<Transfer start>

Start initialization

Set data transfer/receive format in

SMR and SCMR

No

Yes

Set value in BRR

Clear TE and RE bits in SCR to 0

[2]

[3]

Set TE and RE bits in SCR to 1, and

set RIE, TIE, TEIE, and MPIE bits

[4]

1-bit interval elapsed?

Set CKE1 and CKE0 bits in SCR

(TE and RE bits are 0)

[1]

[1] Set the clock selection in SCR. Be sure

to clear bits RIE, TIE, TEIE, and MPIE,

TE and RE to 0.

[2] Set the data transfer/receive format in

SMR and SCMR.

[3] Write a value corresponding to the bit

rate to BRR. This step is not necessary

if an external clock is used.

[4] Wait at least one bit interval, then set the

TE bit or RE bit in SCR to 1.

Also set the RIE, TIE TEIE, and MPIE

bits.

Setting the TE and RE bits enables the

TxD and RxD pins to be used.

Note: * In simultaneous transmit and receive operations, the TE and RE bits should both

be cleared

Figure 12.15 Sample SCI Initialization Flowchart