AMD Geode™ SC2200 Processor Data Book 139

SuperI/O Module

32580B

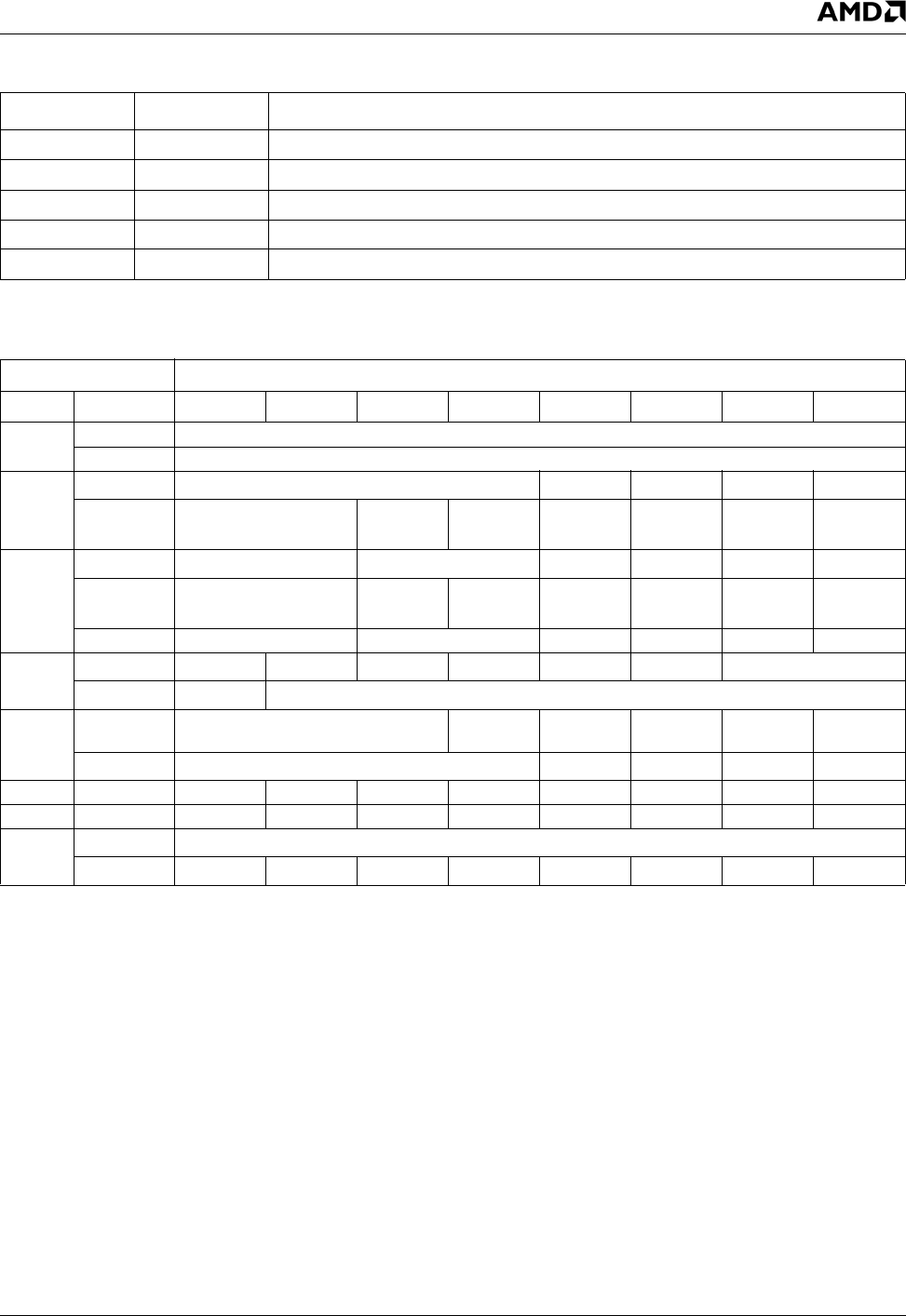

Table 5-41. Bank 3 Register Map

Offset Type Name

00h RO MRID. Module and Revision ID

01h RO SH_LCR. Shadow of LCR

02h RO SH_FCR. Shadow of FIFO Control

03h R/W BSR. Bank Select

04h-07h --- RSVD. Reserved

Table 5-42. Bank 0 Bit Map

Register Bits

OffsetName76543210

00h RXD RXD[7:0] (Receiver Data Bits)

TXD TXD[7:0] (Transmitter Data Bits)

01h

IER

1

RSVD MS_IE LS_IE TXLDL_IE RXHDL_IE

IER

2

RSVD TXEMP_IE

RSVD

3

/

DMA_IE

4

MS_IE LS_IE TXLDL_IE RXHDL_IE

02h

EIR

1

FEN[1:0] RSVD RXFT IPR1 IPR0 IPF

EIR

2

RSVD TXEMP_EV

RSVD

3

/

DMA_EV

4

MS_EV LS_EV or

TXHLT_EV

TXLDL_EV RXHDL_EV

FCR RXFTH[1:0] TXFTH[1:0] RSVD TXSR RXSR FIFO_EN

03h

LCR

5

BKSE SBRK STKP EPS PEN STB WLS[1:0]

BSR

5

BKSE BSR[6:0] (Bank Select)

04h

MCR

1

RSVD LOOP ISEN or

DCDLP

RILP RTS DTR

MCR

2

RSVD TX_DFR RSVD RTS DTR

05h LSR ER_INF TXEMP TXRDY BRK FE PE OE RXDA

06h MSR DCD RI DSR CTS DDCD TERI DDSR DCTS

07h

SPR

1

Scratch Data

ASCR

2

RSVD

TXUR

4

RXACT

4

RXWDG

4

RSVD

S_OET

4

RSVD RXF_TOUT

1. Non-Extended Mode.

2. Extended Mode.

3. In SP1 only.

4. In SP2 only.

5. When bit 7 of this register is set to 1, bits [6:0] of BSR select the bank, as shown in Table 5-38 on page 139.