AMD Geode™ SC2200 Processor Data Book 257

Core Logic Module - SMI Status and ACPI Registers - Function 1

32580B

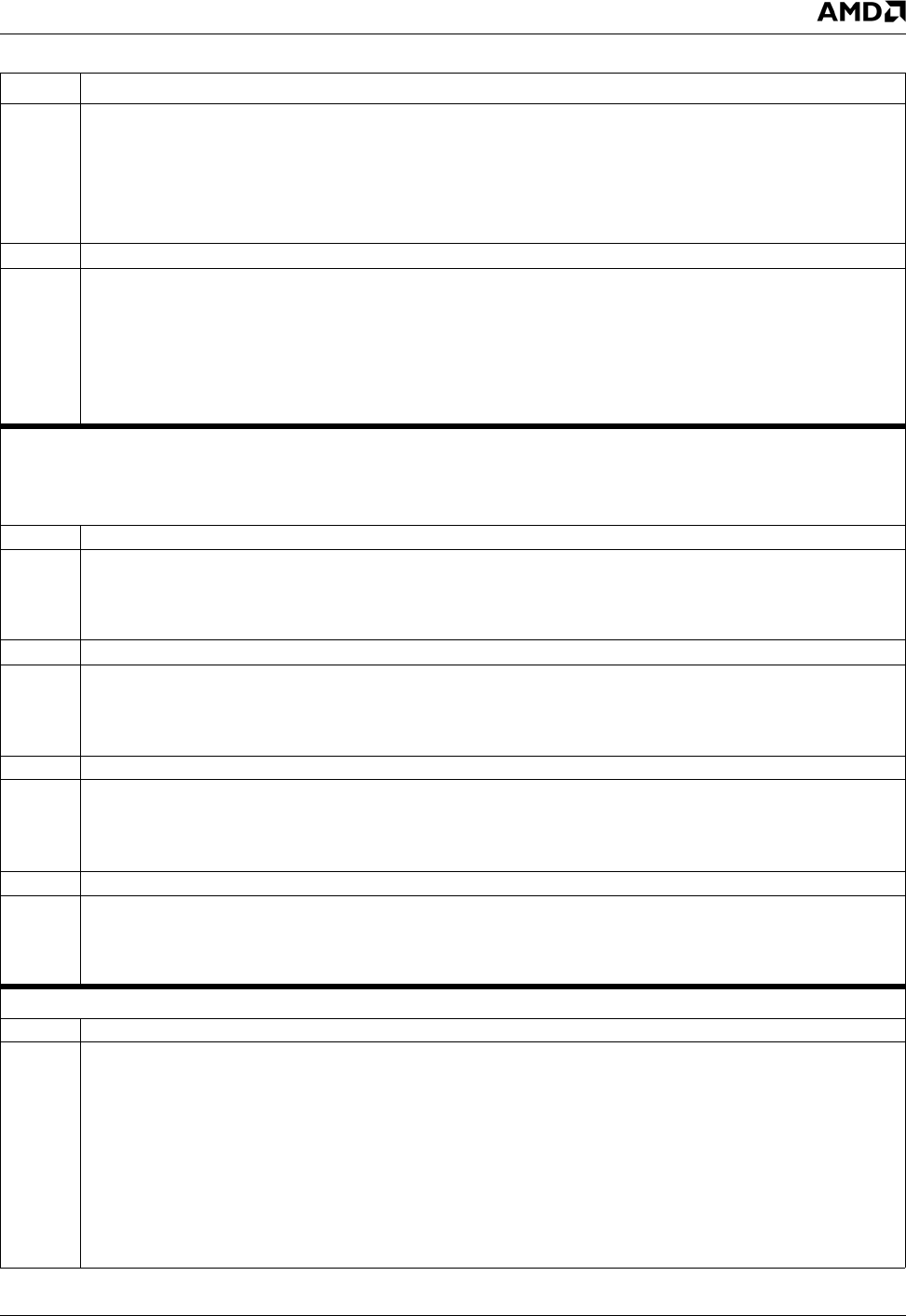

4 BM_STS (Bus Master Status). Indicates if PME was caused by a system bus master requesting the system bus.

0: No.

1: Yes.

For the PME to generate an SCI, set F1BAR1+I/O Offset 0Ch[1] = 1 and F1BAR1+I/O Offset 0Ch[0] = 1. (See Note 2 in the

general description of this register.)

Write 1 to clear.

3:1 Reserved. Must be set to 0.

0 TMR_STS (Timer Carry Status). Indicates if SCI was caused by an MSB toggle (MSB changes from low-to-high or high-to-

low) on the ACPI Timer (F1BAR0+I/O Offset 1Ch or F1BAR1+I/O Offset 1Ch).

0: No.

1: Yes.

For the PME to generate an SCI, set F1BAR1+I/O Offset 0Ah[0] = 1 and F1BAR1+I/O Offset 0Ch[0] = 1. (See Note 2 in the

general description of this register.)

Write 1 to clear.

Offset 0Ah-0Bh PM1A_EN — PM1A PME/SCI Enable Register (R/W) Reset Value: 0000h

In order for the ACPI events described below to generate an SCI, the SCI_EN bit must also be set (F1BAR1+I/O Offset 0Ch[0] = 1).

The SCIs enabled via this register are globally enabled by setting F1BAR1+I/O Offset 08h. There is no second level of SCI status report-

ing for these bits.

15:11 Reserved. Must be set to 0.

10 RTC_EN (Real-Time Clock Enable). Allow SCI generation when the RTC generates an alarm (RTC IRQ signal is

asserted).

0: Disable.

1: Enable

9 Reserved. Must be set to 0.

8 PWRBTN_EN (Power Button Enable). Allow SCI generation when PWRBTN# goes low while the system is in a Working

state.

0: Disable.

1: Enable.

7:6 Reserved. Must be set to 0.

5 GBL_EN (Global Lock Enable). Allow SCI generation when the BIOS releases control of the global lock via the BIOS_RLS

(F1BAR1+I/O Offset 0Fh[1] and GBL_STS (F1BAR1+I/O Offset 08h[5]) bits.

0: Disable.

1: Enable.

4:1 Reserved. Must be set to 0.

0 TMR_EN (ACPI Timer Enable). Allow SCI generation for MSB toggles (MSB changes from low-to-high or high-to-low) on

the ACPI Timer (F1BAR0+I/O Offset 1Ch or F1BAR1+I/O Offset 1Ch).

0: Disable.

1: Enable.

Offset 0Ch-0Dh PM1A_CNT — PM1A Control Register (R/W) Reset Value: 0000h

15:14 Reserved. Must be set to 0.

13 SLP_EN (Sleep Enable). (Write Only) Allow the system to sequence into the sleeping state associated with the SLP_TYPx

(bits [12:10]).

0: Disable.

1: Enable.

This is a write only bit and reads of this bit always return a 0.

The ACPI state machine always waits for an SMI (any SMI) to be generated and serviced before transitioning into a Sleep

state.

If F1BAR1+I/O Offset 18h[9] = 1, an SMI is generated when SLP_EN is set.

Top level SMI status is reported at F1BAR0+I/O Offset 00h/02h[2].

Second level SMI status is reported at F1BAR0+I/O Offset 20h/22h[2].

Table 6-34. F1BAR1+I/O Offset: ACPI Support Registers (Continued)

Bit Description