AMD Geode™ SC2200 Processor Data Book 105

SuperI/O Module

32580B

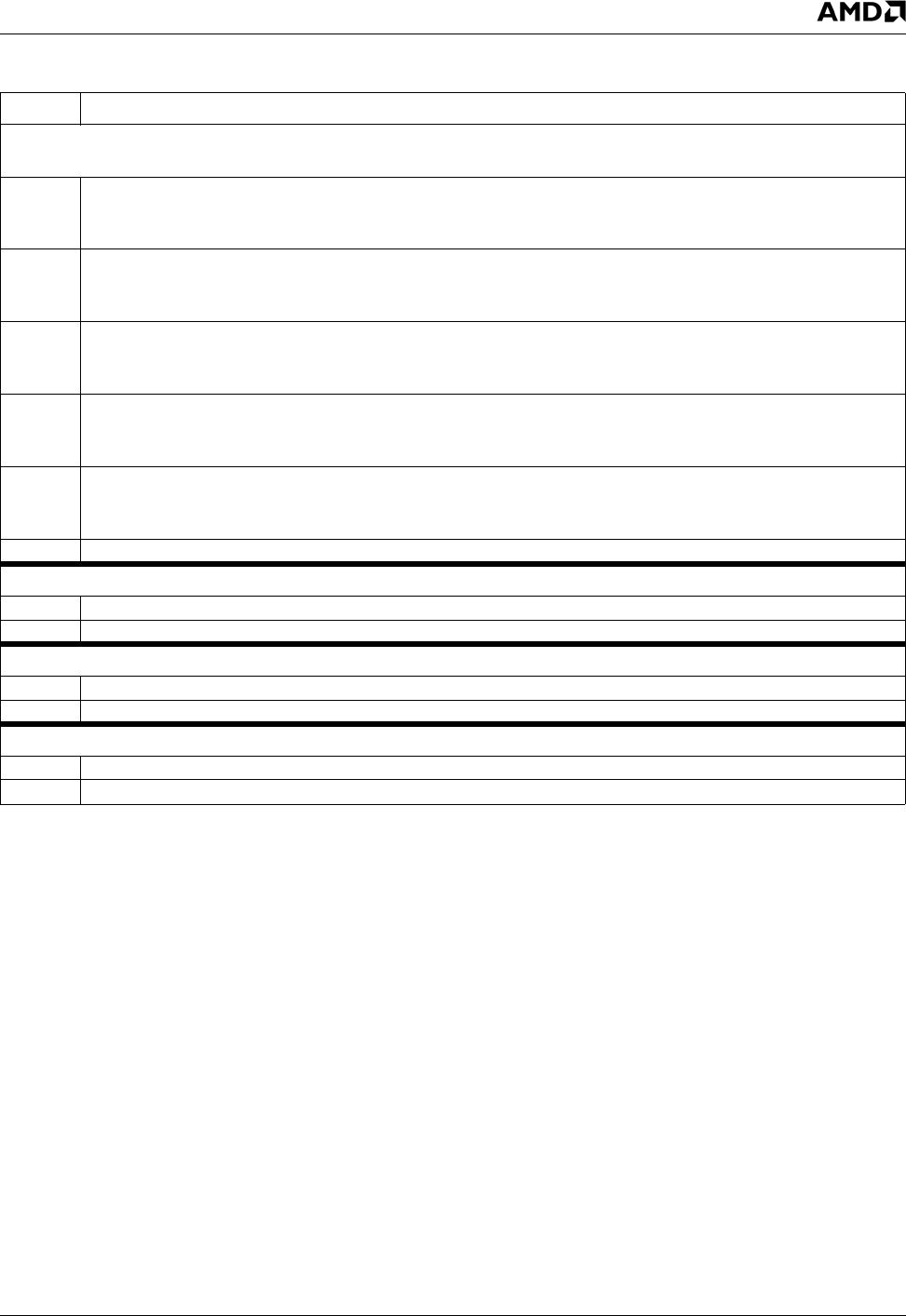

Table 5-7. RTC Configuration Registers

Bit Description

Index F0h RAM Lock Register - RLR (R/W)

When any non-reserved bit in this register is set to 1, it can be cleared only by hardware reset.

7 Block Standard RAM.

0: No effect on Standard RAM access. (Default)

1: Read and write to locations 38h-3Fh of the Standard RAM are blocked, writes ignored, and reads return FFh.

6 Block RAM Write.

0: No effect on RAM access. (Default)

1: Writes to RAM (Standard and Extended) are ignored.

5 Block Extended RAM Write. This bit controls writes to bytes 00h-1Fh of the Extended RAM.

0: No effect on the Extended RAM access. (Default)

1: Writes to bytes 00h-1Fh of the Extended RAM are ignored.

4 Block Extended RAM Read. This bit controls read from bytes 00h-1Fh of the Extended RAM.

0: No effect on Extended RAM access. (Default)

1: Reads to bytes 00h-1Fh of the Extended RAM are ignored.

3 Block Extended RAM. This bit controls access to the Extended RAM 128 bytes.

0: No effect on Extended RAM access. (Default)

1: Read and write to the Extended RAM are blocked: writes are ignored and reads return FFh.

2:0 Reserved.

Index F1h Date Of Month Alarm Register Offset Register - DOMAO (R/W)

7 Reserved.

6:0 Date of Month Alarm Register Offset Value.

Index F2h Month Alarm Register Offset Register - MANAO (R/W)

7 Reserved.

6:0 Month Alarm Register Offset Value.

Index F3h Century Register Offset Register - CENO (R/W)

7 Reserved.

6:0 Century Register Offset Value.