AMD Geode™ SC2200 Processor Data Book 273

Core Logic Module - Audio Registers - Function 3

32580B

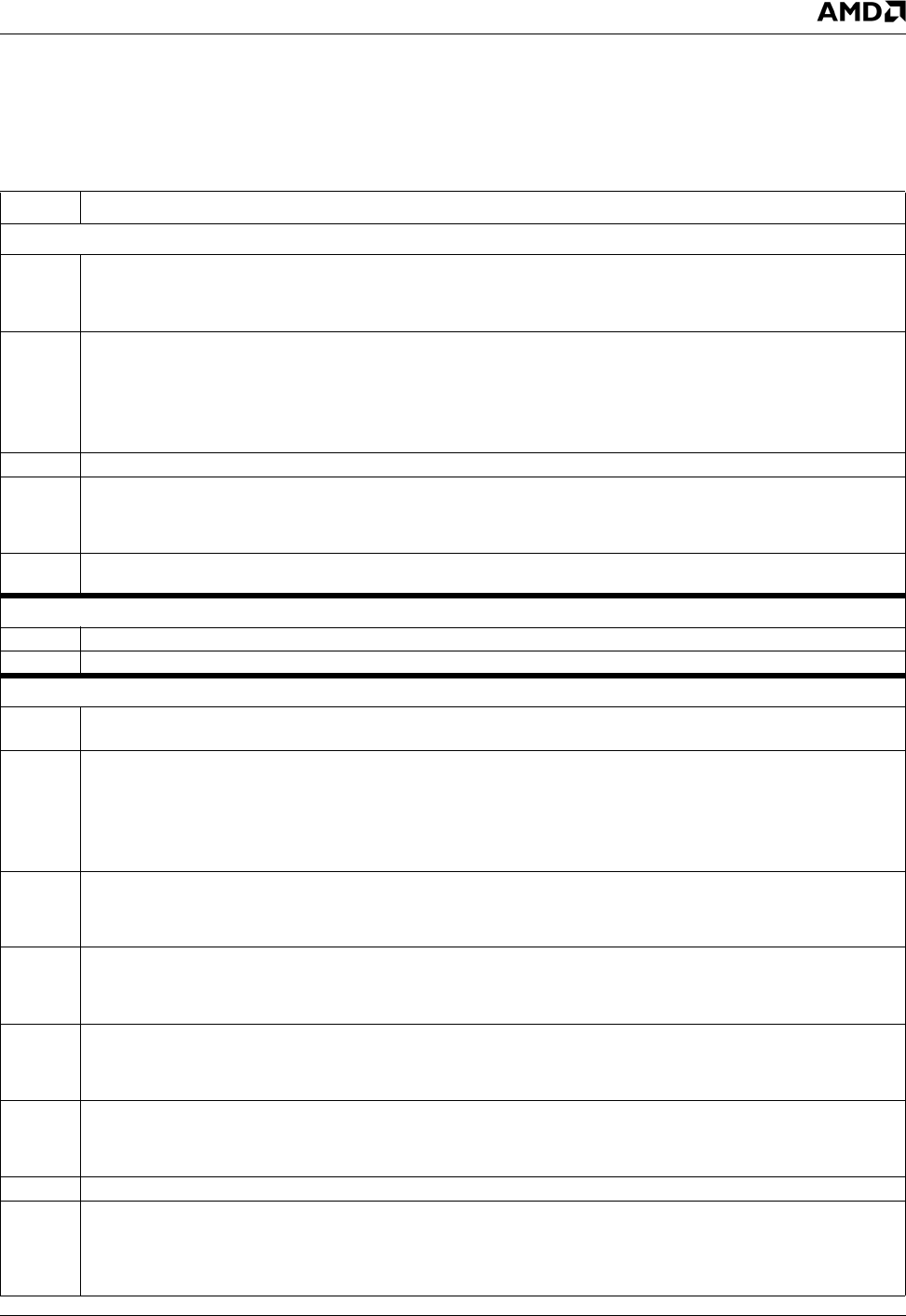

6.4.4.1 Audio Support Registers

F3 Index 10h, Base Address Register 0 (F3BAR0), points

to the base address of where the registers for audio sup-

port are located. Table 6-38 gives the bit formats of the

memory mapped audio configuration registers that are

accessed through F3BAR0.

Table 6-38. F3BAR0+Memory Offset: Audio Configuration Registers

Bit Description

Offset 00h-03h Codec GPIO Status Register (R/W) Reset Value: 00000000h

31 Codec GPIO Interface.

0: Disable.

1: Enable.

30 Codec GPIO SMI. When asserted, allows codec GPIO interrupt to generate an SMI.

0: Disable.

1: Enable.

Top level SMI status is reported at F1BAR0+I/O Offset 00h/02h[1].

Second level SMI status is reported at F3BAR0+Memory Offset 10h/12h[1].

29:21 Reserved. Must be set to 0.

20 Codec GPIO Status Valid. (Read Only) Indicates if the status read is valid.

0: Yes.

1: No.

19:0 Codec GPIO Pin Status. (Read Only) This field indicates the GPIO pin status that is received from the codec in slot 12 on

the SDATA_IN signal.

Offset 04h-07h Codec GPIO Control Register (R/W) Reset Value: 00000000h

31:20 Reserved. Must be set to 0.

19:0 Codec GPIO Pin Data. This field indicates the GPIO pin data that is sent to the codec in slot 12 on the SDATA_OUT signal.

Offset 08h-0Bh Codec Status Register (R/W) Reset Value: 00000000h

31:24 Codec Status Address. (Read Only) Address of the register for which status is being returned. This address comes from

slot 1 bits [19:12].

23 Codec Serial INT Enable. When asserted, allows codec serial interrupt to cause an SMI.

0: Disable.

1: Enable.

Top level SMI status is reported at F1BAR0+I/O Offset 00h/02h[1].

Second level SMI status is reported at F3BAR0+Memory Offset 10h/12h[1].

22 SYNC Pin. Sets SYNC high or low.

0: Low.

1: High.

21 SDATA_IN2_EN. When enabled, allows use of SDATA_IN2 input.

0: Disable.

1: Enable.

20 Audio Bus Master 5 AC97 Slot Select. Selects slot for Audio Bus Master 5 to receive data.

0: Slot 6.

1: Slot 11.

19 Audio Bus Master 4 AC97 Slot Select. Selects slot for Audio Bus Master 4 to transmit data.

0: Slot 6.

1: Slot 11.

18 Reserved. Must be set to 0.

17 Status Tag. (Read Only) The codec status data in bits [15:0] of this register is updated in the current AC97 frame. (codec

ready, slot1 and slot2 bits in tag slot are all set in current AC97 frame).

0: Not new.

1: New, updated in current frame.