208 AMD Geode™ SC2200 Processor Data Book

Core Logic Module - Bridge, GPIO, and LPC Registers - Function 0

32580B

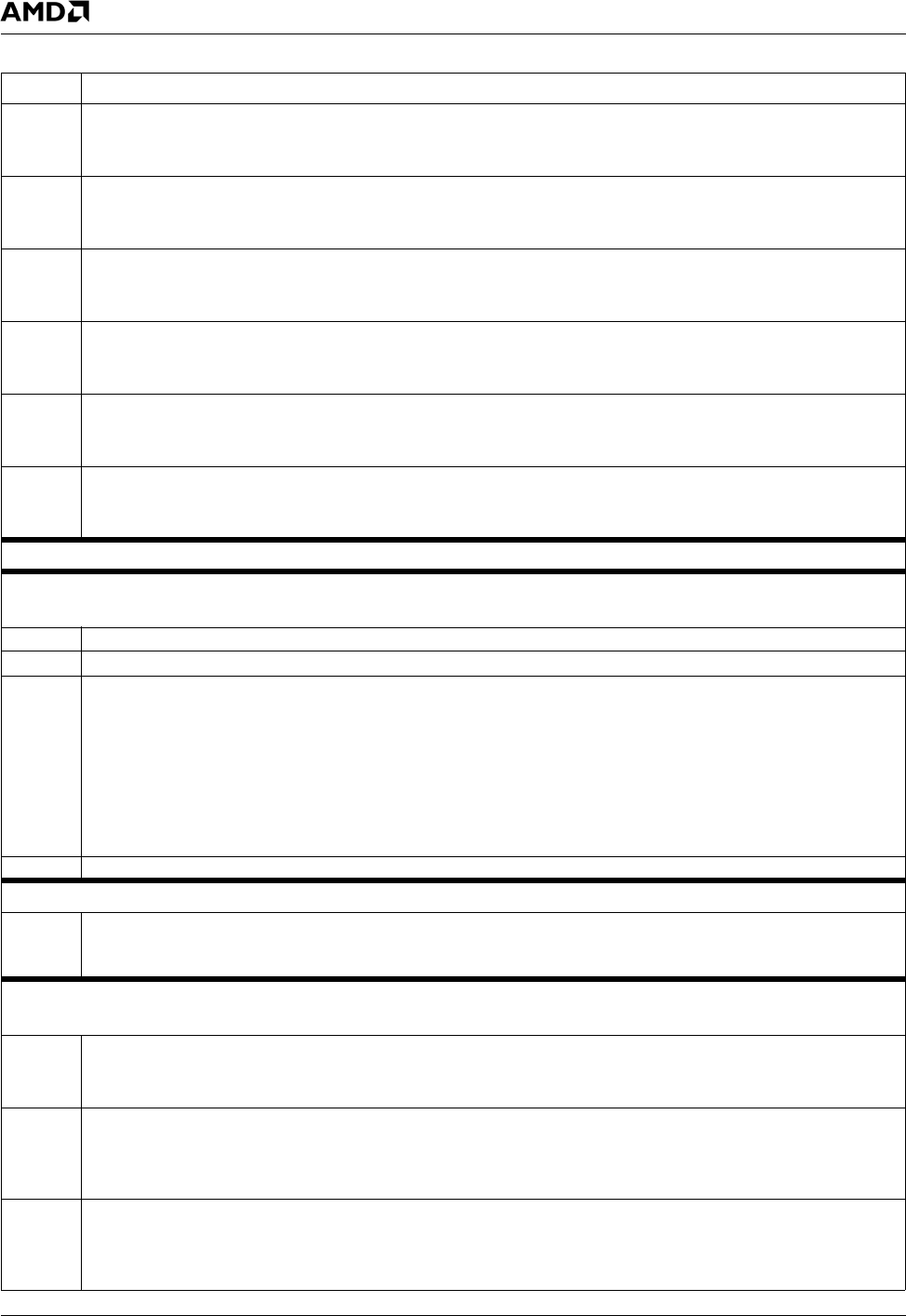

5 SUSP_3V Shut Down PLL3. Allow internal SUSP_3V to shut down PLL3.

0: Clock generator is stopped when internal SUSP_3V is active.

1: Clock generator continues working when internal SUSP_3V is active..

4 SUSP_3V Shut Down PLL2. Allow internal SUSP_3V to shut down PLL2.

0: Clock generator is stopped when internal SUSP_3V is active.

1: Clock generator continues working when internal SUSP_3V is active.

3 SUSP_3V Shut Down PLL6. Allow internal SUSP_3V to shut down PLL6.

0: Clock generator is stopped when internal SUSP_3V is active.

1: Clock generator continues working when internal SUSP_3V is active.

2 ACPI C3 SUSP_3V Enable. Allow internal SUSP_3V to be active during C3 state.

0: Disable.

1: Enable.

1 ACPI SL1 SUSP_3V Enable. Allow internal SUSP_3V to be active during SL1 sleep state.

0: Disable.

1: Enable.

0 ACPI C3 Support Enable. Allow support of C3 states.

0: Disable.

1: Enable.

Index 64h-6Bh Reserved Reset Value: 00h

Index 6Ch-6Fh ROM Mask Register (R/W) Reset Value: 0000FFF0h

Note: Register must be read/written as a DWORD.

31:16 Reserved. Must be written to 0.

15:8 Reserved. Must be written to FFh.

7:4 ROM Size. If F0 Index 52h[2] = 1:

0000: 16 MB = FF000000h-FFFFFFFFh

1000: 8 MB = FF800000h-FFFFFFFFh

1100: 4 MB = FFC00000h-FFFFFFFFh

1110: 2 MB = FFE00000h-FFFFFFFFh

1111: 1 MB = FFF00000h-FFFFFFFFh

All other settings for these bits are reserved.

3:0 Reserved. Must be written to 0.

Index 70h-71h IOCS1# Base Address Register (R/W) Reset Value: 0000h

15:0 I/O Chip Select 1 Base Address. This 16-bit value represents the I/O base address used to enable assertion of IOCS1#

(ball D10 or N30 - see PMR[23] in Table 4-2 on page 76).

This register is used in conjunction with F0 Index 72h (IOCS1# Control register).

Index 72h IOCS1# Control Register (R/W) Reset Value: 00h

This register is used in conjunction with F0 Index 70h (IOCS1# Base Address register).

7 I/O Chip Select 1 Positive Decode (IOCS1#).

0: Disable.

1: Enable.

6 Writes Result in Chip Select. When this bit is set to 1, writes to configured I/O address (base address configured in F0

Index 70h; range configured in bits [4:0]) cause IOCS1# to be asserted.

0: Disable.

1: Enable.

5 Reads Result in Chip Select. When this bit is set to 1, reads from configured I/O address (base address configured in F0

Index 70h; range configured in bits [4:0]) cause IOCS1# to be asserted.

0: Disable.

1: Enable.

Table 6-29. F0: PCI Header/Bridge Configuration Registers for GPIO and LPC Support (Continued)

Bit Description