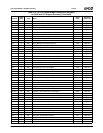

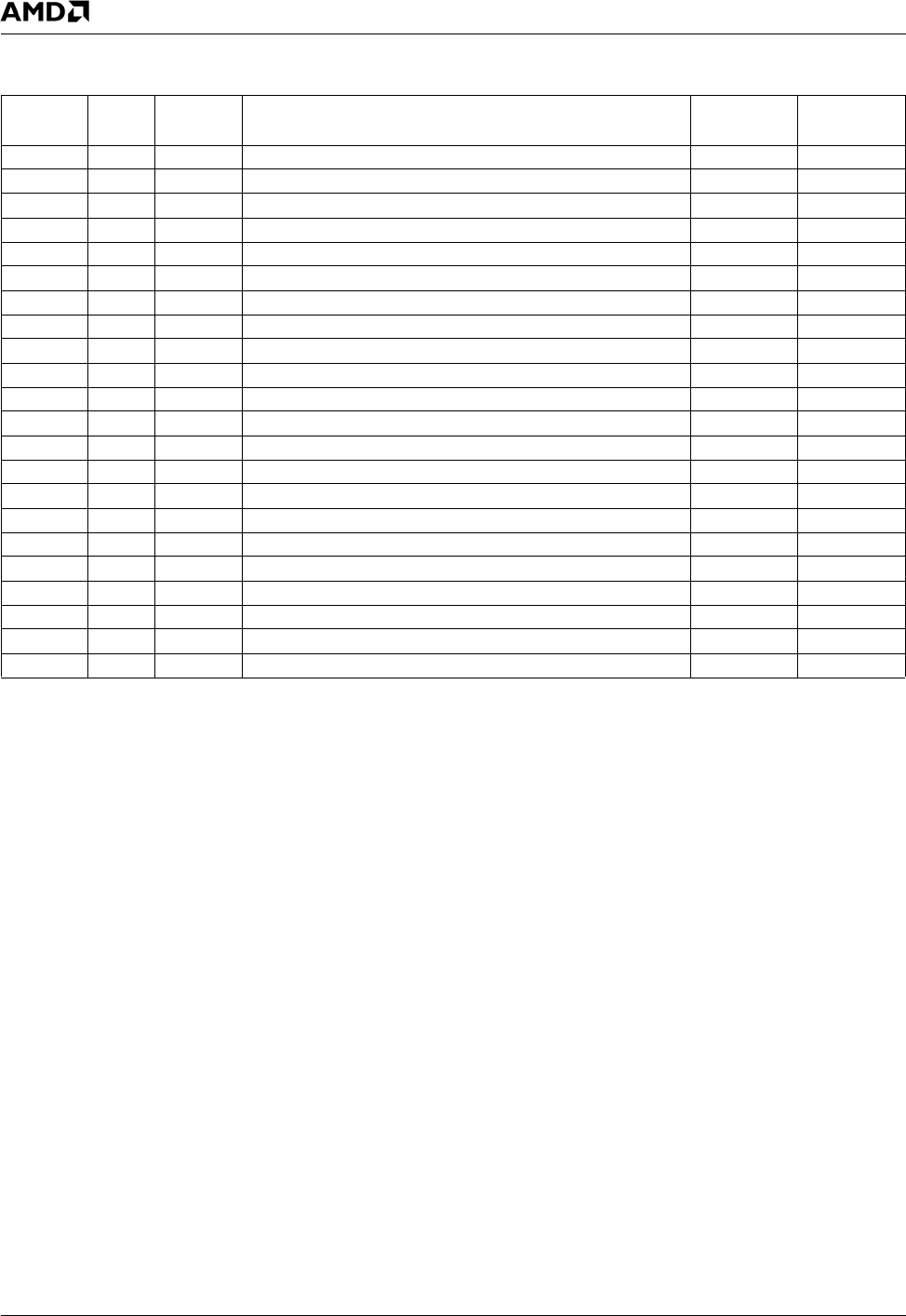

186 AMD Geode™ SC2200 Processor Data Book

Core Logic Module - Register Summary

32580B

B8h 8 RO DMA Shadow Register xxh Page 225

B9h 8 RO PIC Shadow Register xxh Page 225

BAh 8 RO PIT Shadow Register xxh Page 226

BBh 8 RO RTC Index Shadow Register xxh Page 226

BCh 8 R/W Clock Stop Control Register 00h Page 226

BDh-BFh --- --- Reserved 00h Page 226

C0h-C3h 32 R/W User Defined Device 1 Base Address Register 00000000h Page 226

C4h-C7h 32 R/W User Defined Device 2 Base Address Register 00000000h Page 227

C8h-CBh 32 R/W User Defined Device 3 Base Address Register 00000000h Page 227

CCh 8 R/W User Defined Device 1 Control Register 00h Page 227

CDh 8 R/W User Defined Device 2 Control Register 00h Page 227

CEh 8 R/W User Defined Device 3 Control Register 00h Page 228

CFh --- --- Reserved 00h Page 228

D0h 8 WO Software SMI Register 00h Page 228

D1h-EBh 16 --- Reserved 00h Page 228

ECh 8 R/W Timer Test Register 00h Page 228

EDh-F3h --- --- Reserved 00h Page 228

F4h 8 RC Second Level PME/SMI Status Register 1 00h Page 228

F5h 8 RC Second Level PME/SMI Status Register 2 00h Page 229

F6h 8 RC Second Level PME/SMI Status Register 3 00h Page 230

F7h 8 RC Second Level PME/SMI Status Register 4 00h Page 231

F8h-FFh --- --- Reserved 00h Page 232

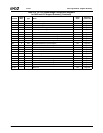

Table 6-14. F0: PCI Header/Bridge Configuration Registers

for GPIO and LPC Support Summary (Continued)

F0 Index

Width

(Bits) Type Name

Reset

Value

Reference

(Table 6-29)