238 AMD Geode™ SC2200 Processor Data Book

Core Logic Module - Bridge, GPIO, and LPC Registers - Function 0

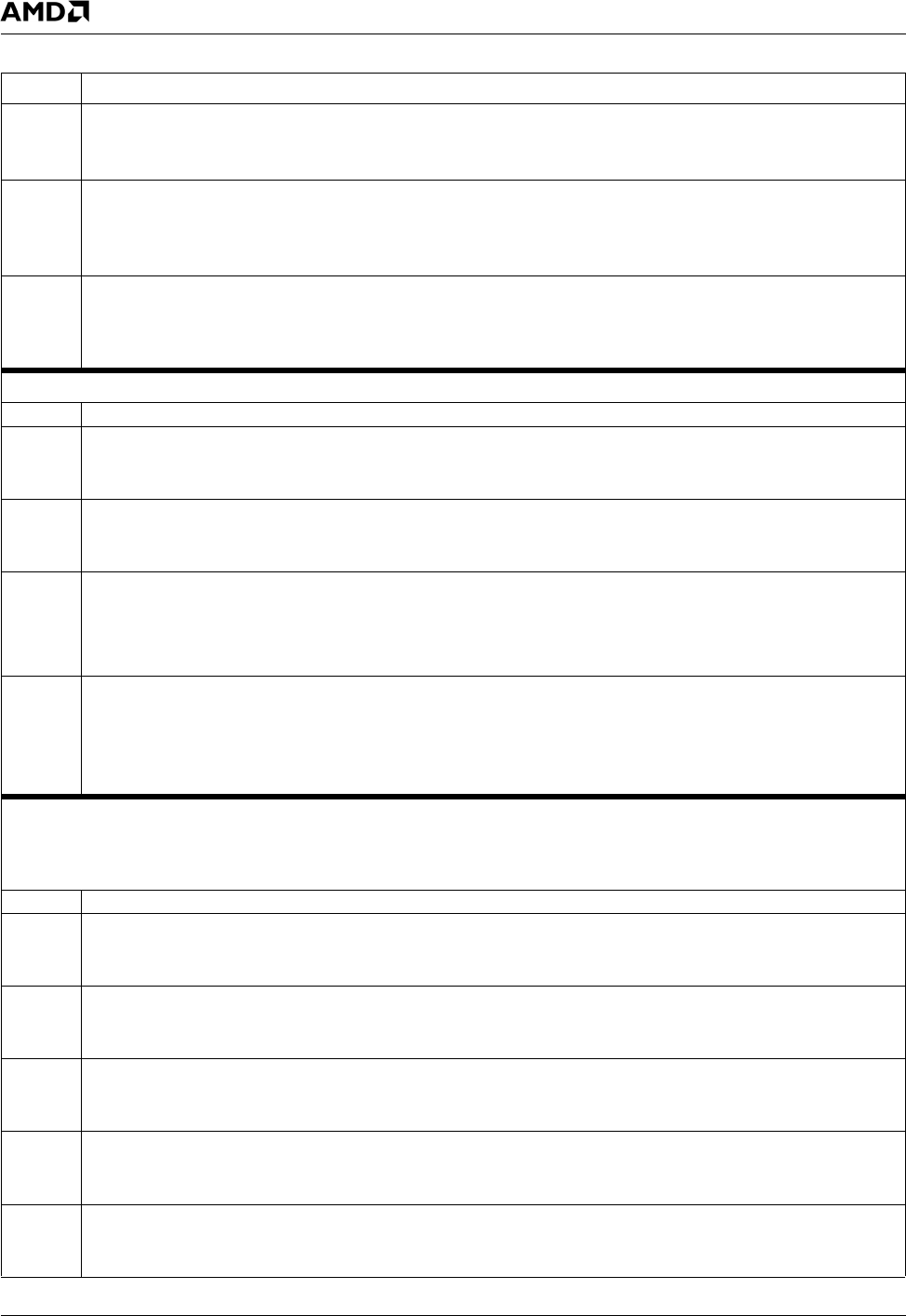

32580B

2 SMI# Polarity. This bit allows signal polarity selection of the SMI# generated from LPC.

0: Active high.

1: Active low.

1 IRQ1 Polarity. If LPC is selected as the interface source for IRQ1 (F0BAR1+I/O Offset 00h[1] = 1), this bit allows signal

polarity selection.

0: Active high.

1: Active low.

0 IRQ0 Polarity. If LPC is selected as the interface source for IRQ0 (F0BAR1+I/O Offset 00h[0] = 1), this bit allows signal

polarity selection.

0: Active high.

1: Active low.

Offset 08h-0Bh SERIRQ_CNT — Serial IRQ Control Register (R/W) Reset Value: 00000000h

31:8 Reserved.

7 Serial IRQ Enable.

0: Disable.

1: Enable.

6 Serial IRQ Interface Mode.

0: Continuous.

1: Quiet.

5:2 Number of IRQ Data Frames.

0000: 17 frames 0100: 21 frames 1000: 25 frames 1100: 29 frames

0001: 18 frames 0101: 22 frames 1001: 26 frames 1101: 30 frames

0010: 19 frames 0110: 23 frames 1010: 27 frames 1110: 31 frames

0011: 20 frames 0111: 24 frames 1011: 28 frames 1111: 32 frames

1:0 Start Frame Pulse Width.

00: 4 Clocks

01: 6 Clocks

10: 8 Clocks

11: Reserved

Offset 0Ch-0Fh DRQ_SRC — DRQ Source Register (R/W) Reset Value: 00000000h

Note: DRQx are internal signals between the Core Logic and SuperI/O modules. Some signals require additional programming to

make them externally accessible. See Table 4-2 "Multiplexing, Interrupt Selection, and Base Address Registers" on page 76 for

pin multiplexing details and Table 3-4 "Strap Options" on page 45 for LPC_ROM strap information.

31:8 Reserved.

7 DRQ7 Source. Selects the interface source of the DRQ7 signal.

0: ISA - DRQ7 (unavailable externally).

1: LPC - LDRQ# (ball L28).

6 DRQ6 Source. Selects the interface source of the DRQ6 signal.

0: ISA - DRQ6 (unavailable externally).

1: LPC - LDRQ# (ball L28).

5 DRQ5 Source. Selects the interface source of the DRQ5 signal.

0: ISA - DRQ5 (unavailable externally).

1: LPC - LDRQ# (ball L28).

4 LPC BM0 Cycles. Allow LPC Bus Master 0 Cycles.

0: Enable.

1: Disable.

3 DRQ3 Source. Selects the interface source of the DRQ3 signal.

0: ISA - DRQ3 (unavailable externally).

1: LPC - LDRQ# (ball L28).

Table 6-31. F0BAR1+I/O Offset: LPC Interface Configuration Registers (Continued)

Bit Description