180 AMD Geode™ SC2200 Processor Data Book

Core Logic Module

32580B

Fast Path Write captures the data and address bit 1 (A1) of

the first access, but does not generate an SMI. A1 is stored

in F3BAR0+Memory Offset 14h[15]. The second access

causes an SMI, and the data and address are captured as

in a normal trapped I/O.

In Fast Path Write, the Core Logic module responds to

writes to the following addresses:

388h, 38Ah, 38Bh, 2x0h, 2x2h, and 2x8h

Table 6-38 on page 273 shows the bit formats of the sec-

ond level SMI status reporting registers and the Fast Path

Read/Write programming bits.

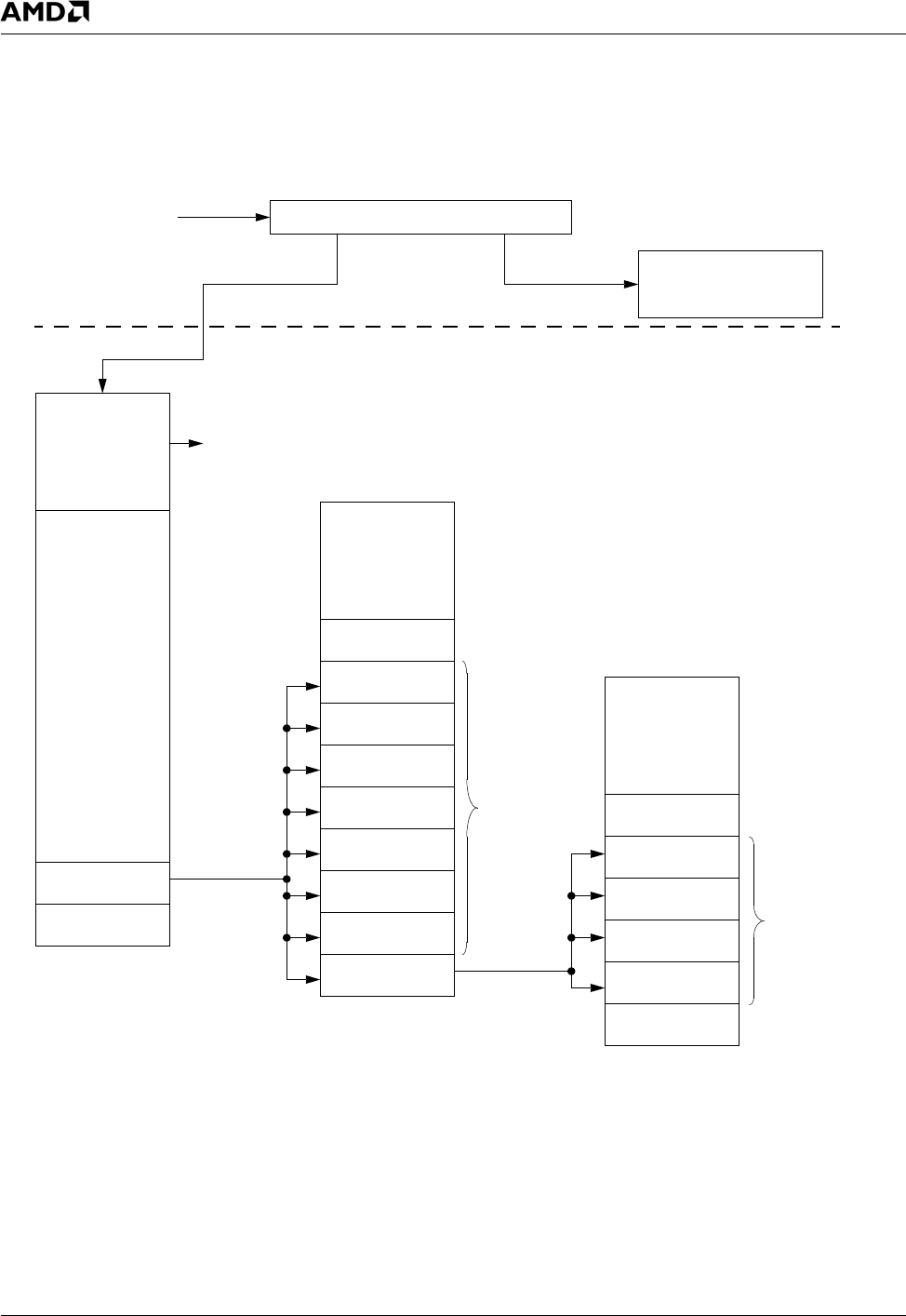

Figure 6-14. Audio SMI Tree Example

SMI# Asserted SMM software reads SMI Header

If Bit X = 0

(Internal SMI)

If Bit X = 1

(External SMI)

Call internal SMI handler

to take appropriate action

GX1

Core Logic Module

F1BAR0+Memory

Read to Clear

to determine

top-level source

of SMI

F3BAR0+Memory

Offset 10h

Read to Clear

SMI De-asserted after all SMI Sources are Cleared

Bit 7

ABM5_SMI

Bits [15:2]

Bit 0

Bit 1

AUDIO_SMI

Offset 02h

Module

to determine

second-level

source of SMI

Bits [15:8]

Bit 6

ABM4_SMI

Bit 5

ABM3_SMI

Bit 4

ABM2_SMI

Bit 3

ABM1_SMI

Bit 2

ABM0_SMI

Bit 1

SER_INTR_SMI

Bit 0

I/O_TRAP_SMI

F3BAR0+Memory

Offset 14h

Read to Clear

to determine

third-level

source of SMI

Bit 13

SMI_SC/FM_TRAP

Bits [31:14]

Bit 12

SMI_DMA_TRAP

Bit 11

SMI_MPU_TRAP

Bit 10

SMI_SC/FM_TRAP

Bits [9:0]

(i.e., Top, Second, and Third Levels)

Take

Appropriate

Action

Take

Appropriate

Action

Other_SMI

Other_SMI

RSVD

Other_RO

Other_RO

Top Level

Second Level

Third Level

If bit 1 = 1,

Source of

SMI is

If bit 0 = 1,

Source of

SMI is

I/O Trap

Audio Event