AMD Geode™ SC2200 Processor Data Book 295

Core Logic Module - USB Controller Registers - PCIUSB

32580B

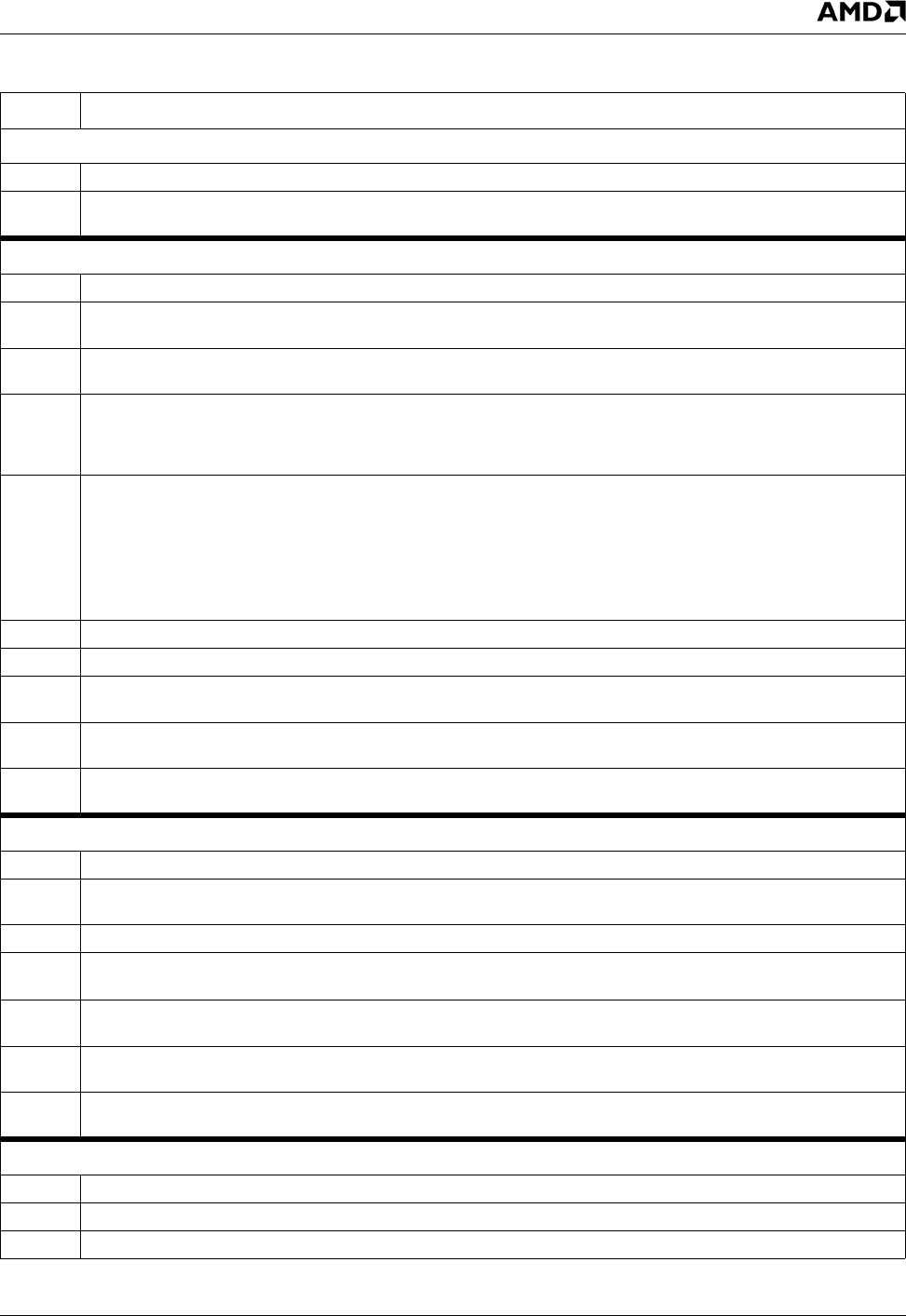

Table 6-42. USB_BAR+Memory Offset: USB Controller Registers

Bit Description

Offset 00h-03h HcRevision Register (RO) Reset Value = 00000110h

31:8 Reserved. Read/Write 0s.

7:0 Revision (Read Only). Indicates the Open HCI Specification revision number implemented by the Hardware. USB sup-

ports 1.0 specification. (X.Y = XYh).

Offset 04h-07h HcControl Register (R/W) Reset Value = 00000000h

31:11 Reserved. Read/Write 0s.

10 RemoteWakeupConnectedEnable. If a remote wakeup signal is supported, this bit enables that operation. Since there is

no remote wakeup signal supported, this bit is ignored.

9 RemoteWakeupConnected (Read Only). This bit indicated whether the HC supports a remote wakeup signal. This imple-

mentation does not support any such signal. The bit is hard-coded to 0.

8 InterruptRouting. This bit is used for interrupt routing:

0: Interrupts routed to normal interrupt mechanism (INT).

1: Interrupts routed to SMI.

7:6 HostControllerFunctionalState. This field sets the HC state. The HC may force a state change from UsbSuspend to

UsbResume after detecting resume signaling from a downstream port. States are:

00: UsbReset.

01: UsbResume.

10: UsbOperational.

11: UsbSuspend.

5 BulkListEnable. When set, this bit enables processing of the Bulk list.

4 ControlListEnable. When set, this bit enables processing of the Control list.

3 IsochronousEnable. When clear, this bit disables the Isochronous List when the Periodic List is enabled (so Interrupt EDs

may be serviced). While processing the Periodic List, the HC will check this bit when it finds an isochronous ED.

2 PeriodicListEnable. When set, this bit enables processing of the Periodic (interrupt and isochronous) list. The HC checks

this bit prior to attempting any periodic transfers in a frame.

1:0 ControlBulkServiceRatio. Specifies the number of Control Endpoints serviced for every Bulk Endpoint. Encoding is N-1

where N is the number of Control Endpoints (i.e., 00: 1 Control Endpoint; 11: 3 Control Endpoints).

Offset 08h-0Bh HcCommandStatus Register (R/W) Reset Value = 00000000h

31:18 Reserved. Read/Write 0s.

17:16 ScheduleOverrunCount. This field increments every time the SchedulingOverrun bit in HcInterruptStatus is set. The

count wraps from 11 to 00.

15:4 Reserved. Read/Write 0s.

3 OwnershipChangeRequest. When set by software, this bit sets the OwnershipChange field in HcInterruptStatus. The bit

is cleared by software.

2 BulkListFilled. Set to indicate there is an active ED on the Bulk List. The bit may be set by either software or the HC and

cleared by the HC each time it begins processing the head of the Bulk List.

1 ControlListFilled. Set to indicate there is an active ED on the Control List. It may be set by either software or the HC and

cleared by the HC each time it begins processing the head of the Control List.

0 HostControllerReset. This bit is set to initiate a software reset. This bit is cleared by the HC upon completion of the reset

operation.

Offset 0Ch-0Fh HcInterruptStatus Register (R/W) Reset Value = 00000000h

31 Reserved. Read/Write 0s.

30 OwnershipChange. This bit is set when the OwnershipChangeRequest bit of HcCommandStatus is set.

29:7 Reserved. Read/Write 0s.