AMD Geode™ SC2200 Processor Data Book 103

SuperI/O Module

32580B

5.4.1 SIO Control and Configuration Registers

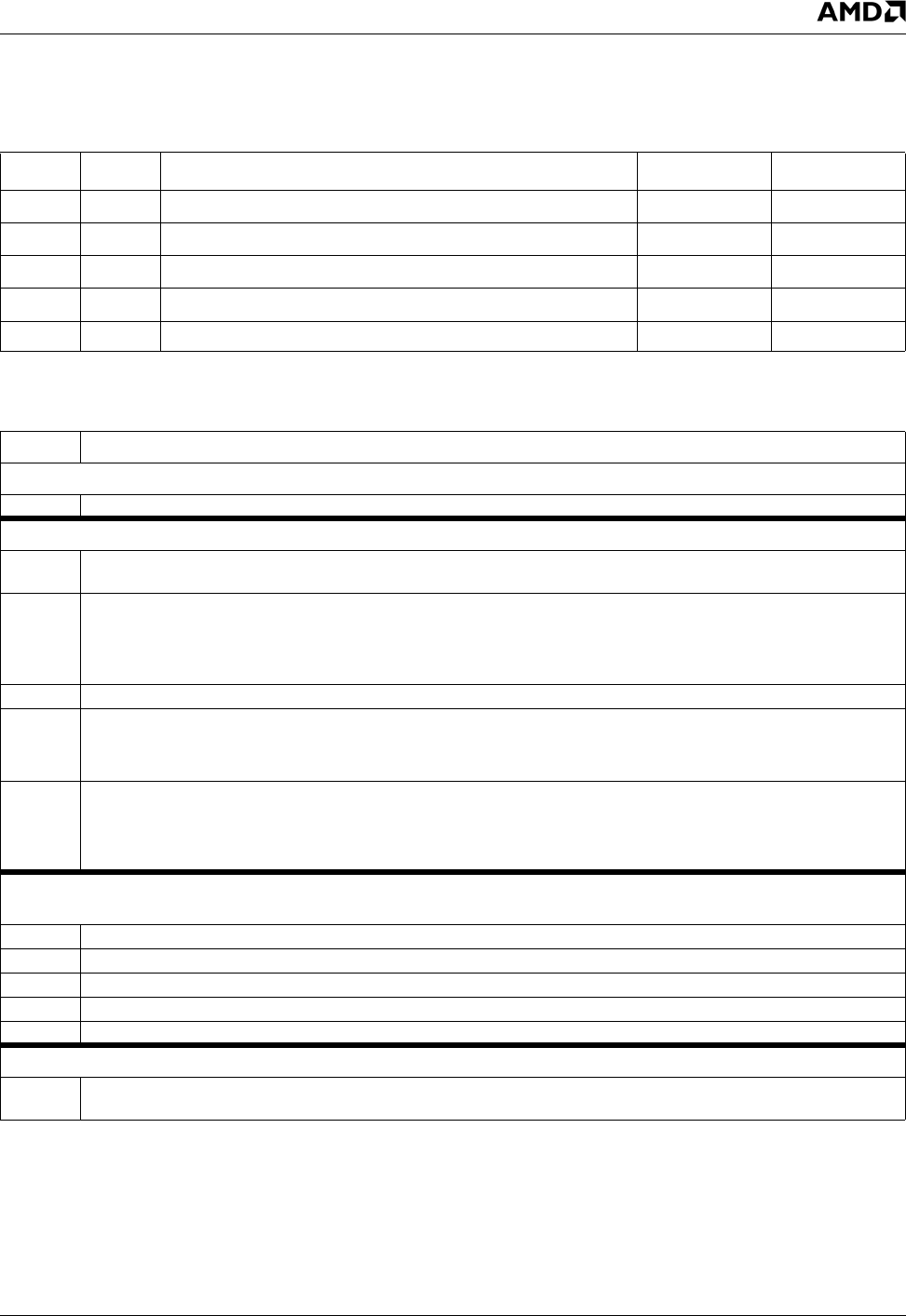

Table 5-4 lists the SIO Control and Configuration registers and Table 5-5 provides their bit formats.

Table 5-4. SIO Control and Configuration Register Map

Index Type Name Power Rail Reset Value

20h RO SID. SIO ID V

CORE

F5h

21h R/W SIOCF1. SIO Configuration 1 V

CORE

01h

22h R/W SIOCF2. SIO Configuration 2 V

PP

02h

27h RO SRID. SIO Revision ID V

CORE

01h

2Eh --- RSVD. Reserved exclusively for AMD use --- ---

Table 5-5. SIO Control and Configuration Registers

Bit Description

Index 20h SIO ID Register - SID (RO) Reset Value: F5h

7:0 Chip ID. Contains the identity number of the module. The SIO module is identified by the value F5h.

Index 21h SIO Configuration 1 Register - SIOCF1 (RW) Reset Value: 01h

7:6 General Purpose Scratch. When bit 5 is set to 1, these bits are RO. After reset, these bits can be read or write. Once

changed to RO, the bits can be changed back to R/W only by a hardware reset.

5 Lock Scratch. This bit controls bits 7 and 6 of this register. Once this bit is set to 1 by software, it can be cleared to 0 only

by a hardware reset.

0: Bits 7 and 6 of this register are R/W bits. (Default)

1: Bits 7 and 6 of this register are RO bits.

4:2 Reserved.

1 SW Reset. Read always returns 0.

0: Ignored. (Default)

1: Resets all devices that are reset by MR (with the exception of the lock bits) and the registers of the SWC.

0 Global Device Enable. This bit controls the function enable of all the logical devices in the SIO module, except the SWC

and the RTC. It allows them to be disabled simultaneously by writing to a single bit.

0: All logical devices in the SIO module are disabled, except the SWC and the RTC.

1: Each logical device is enabled according to its Activate register at Index 30h. (Default)

Index 22h SIO Configuration 2 Register - SIOCF2 (R/W) Reset Value: 02h

Note: This register is reset only when V

PP

is first applied.

7 Reserved.

6:4 General Purpose Scratch. Battery-backed.

3:2 Reserved.

1 Reserved.

0 Reserved. (RO)

Index 27h SIO Revision ID Register - SRID (RO) Reset Value: 01h

7:0 SIO Revision ID. (RO) This RO register contains the identity number of the chip revision. SRID is incremented on each revi-

sion.