AMD Geode™ SC2200 Processor Data Book 397

Electrical Specifications

32580B

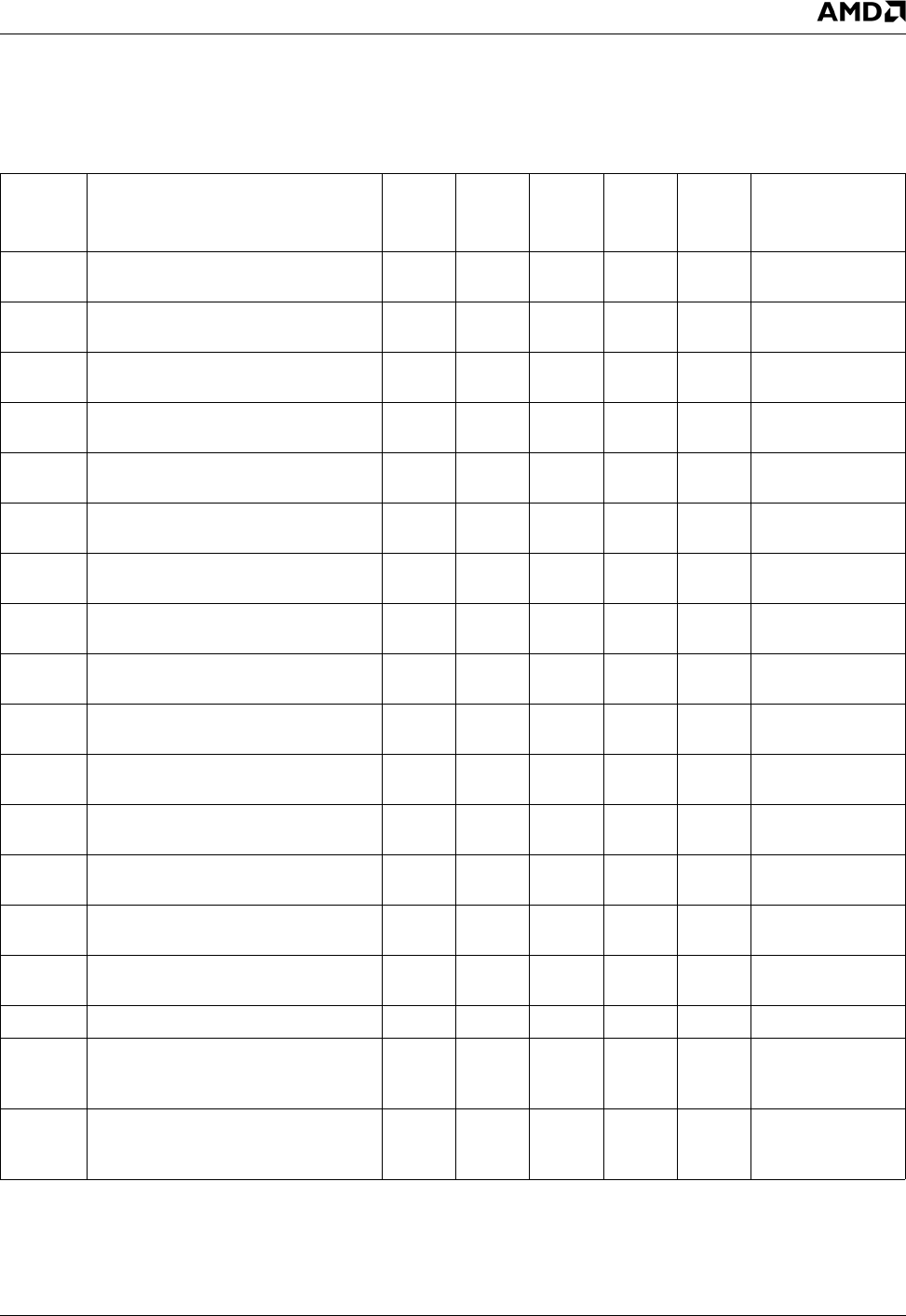

9.3.6 Sub-ISA Interface

All output timing is guaranteed for 50 pF load, unless other-

wise specified.

The ISA Clock divisor (defined in F0 Index 50h[2:0] of the

Core Logic module) is 011.

Table 9-22. Sub-ISA Timing Parameters

Symbol Parameter

Bus

Width

(Bits) Type

Min

(ns)

Max

(ns) Figure Comments

t

RD1

MEMR#/DOCR#/RD#/TRDE# Read

active pulse width FE to RE

16 M 225 9-19 Standard

t

RD2

MEMR#/DOCR#/RD#/TRDE# Read

active pulse width FE to RE

16 M 105 9-19 Zero wait state

t

RD3

IOR#/RD#/TRDE# Read active pulse

width FE to RE

16 I/O 160 9-19 Standard

t

RD4

IOR#/MEMR#/DOCR#/RD#/TRDE#

Read active pulse width FE to RE

8 M, I/O 520 9-19 Standard

t

RD5

IOR#/MEMR#/DOCR#/RD#/TRDE#

Read active pulse width FE to RE

8 M, I/O 160 9-19 Zero wait state

t

RCU1

MEMR#/DOCR#/RD#/TRDE#

inactive pulse width

16 M 103 9-19

t

RCU2

MEMR#/DOCR#/RD#/TRDE#

inactive pulse width

8M163 9-19

t

RCU3

IOR#/RD#/TRDE# inactive pulse

width

8, 16 I/O 163 9-19

t

WR1

MEMW#/WR# Write active pulse

width FE to RE

16 M 225 9-20 Standard

t

WR2

MEMW#/DOCW#/WR# Write active

pulse width FE to RE

16 M 105 9-20 Zero wait state

t

WR3

IOW#/WR# Write active pulse width

FE to RE

16 I/O 160 9-20 Standard

t

WR4

IOW#/MEMW#/DOCW#/WR# Write

active pulse width FE to RE

8 M, I/O 520 9-20 Standard

t

WR5

IOW#/MEMW#/DOCW#/WR# Write

active pulse width FE to RE

8 M, I/O 160 9-20 Zero wait state

t

WCU1

MEMW#/WR#/DOCW# inactive pulse

width

16 M 103 9-20

t

WCU2

MEMW#/WR#/DOCW# inactive pulse

width

8M163 9-20

t

WCU3

IOW#/WR# inactive pulse width 8, 16 I/O 163 9-20

t

RDYH

IOR#/MEMR#/RD#/DOCR#/IOW#/

MEMW#/WR#/DOCW# Hold after

IOCHRDY RE

8, 16 M, I/O 120 9-19

9-20

t

RDYA1

IOCHRDY valid after IOR#/MEMR#/

RD#/DOCR#/IOW#/MEMW#/WR#/

DOCW# FE

16 M, I/O 78 9-19

9-20