AMD Geode™ SC2200 Processor Data Book 253

Core Logic Module - SMI Status and ACPI Registers - Function 1

32580B

15 EXT_SMI7 SMI Status. (Read Only) Indicates whether or not an SMI was caused by an assertion of EXT_SMI7.

0: No.

1: Yes.

To enable SMI generation, set bit 7 to 1.

14 EXT_SMI6 SMI Status. (Read Only) Indicates whether or not an SMI was caused by an assertion of EXT_SMI6.

0: No.

1: Yes.

To enable SMI generation, set bit 6 to 1.

13 EXT_SMI5 SMI Status. (Read Only) Indicates whether or not an SMI was caused by an assertion of EXT_SMI5.

0: No.

1: Yes.

To enable SMI generation, set bit 5 to 1.

12 EXT_SMI4 SMI Status. (Read Only) Indicates whether or not an SMI was caused by an assertion of EXT_SMI4.

0: No.

1: Yes.

To enable SMI generation, set bit 4 to 1.

11 EXT_SMI3 SMI Status. (Read Only) Indicates whether or not an SMI was caused by an assertion of EXT_SMI3.

0: No.

1: Yes.

To enable SMI generation, set bit 3 to 1.

10 EXT_SMI2 SMI Status. (Read Only) Indicates whether or not an SMI was caused by an assertion of EXT_SMI2.

0: No.

1: Yes.

To enable SMI generation, set bit 2 to 1.

9 EXT_SMI1 SMI Status. (Read Only) Indicates whether or not an SMI was caused by an assertion of EXT_SMI1.

0: No.

1: Yes.

To enable SMI generation, set bit 1 to 1.

8 EXT_SMI0 SMI Status. (Read Only) Indicates whether or not an SMI was caused by an assertion of EXT_SMI0.

0: No.

1: Yes.

To enable SMI generation, set bit 0 to 1.

7 EXT_SMI7 SMI Enable. When this bit is asserted, allow EXT_SMI7 to generate an SMI on negative-edge events.

0: Disable.

1: Enable.

Top level SMI status is reported at F1BAR0+00h/02h[10].

Second level SMI status is reported at bits 23 (RC) and 15 (RO).

6 EXT_SMI6 SMI Enable. When this bit is asserted, allow EXT_SMI6 to generate an SMI on negative-edge events.

0: Disable.

1: Enable.

Top level SMI status is reported at F1BAR0+00h/02h[10].

Second level SMI status is reported at bits 22 (RC) and 14 (RO).

5 EXT_SMI5 SMI Enable. When this bit is asserted, allow EXT_SMI5 to generate an SMI on negative-edge events.

0: Disable.

1: Enable.

Top level SMI status is reported at F1BAR0+00h/02h[10].

Second level SMI status is reported at bits 21 (RC) and 13 (RO).

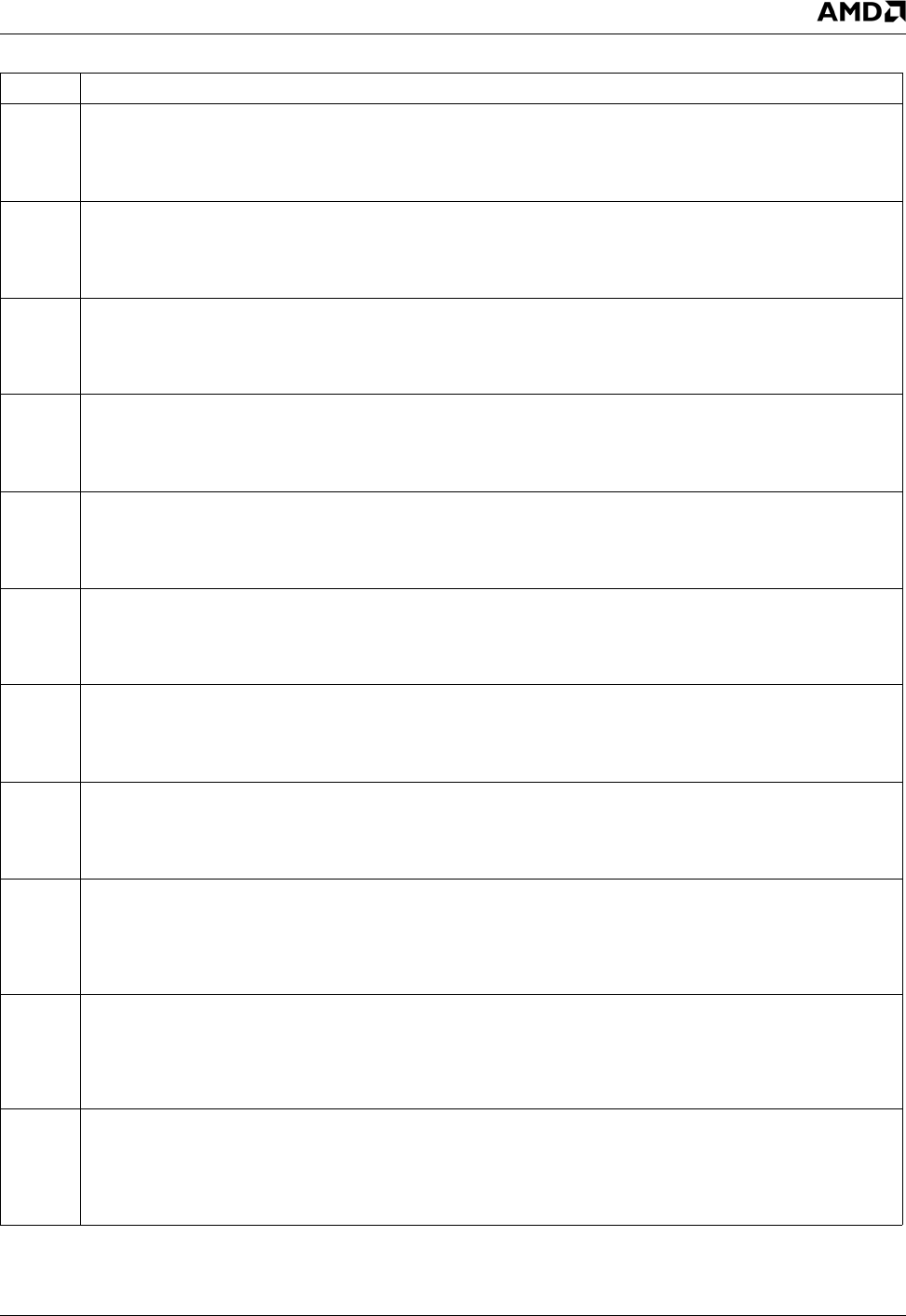

Table 6-33. F1BAR0+I/O Offset: SMI Status Registers (Continued)

Bit Description