254 AMD Geode™ SC2200 Processor Data Book

Core Logic Module - SMI Status and ACPI Registers - Function 1

32580B

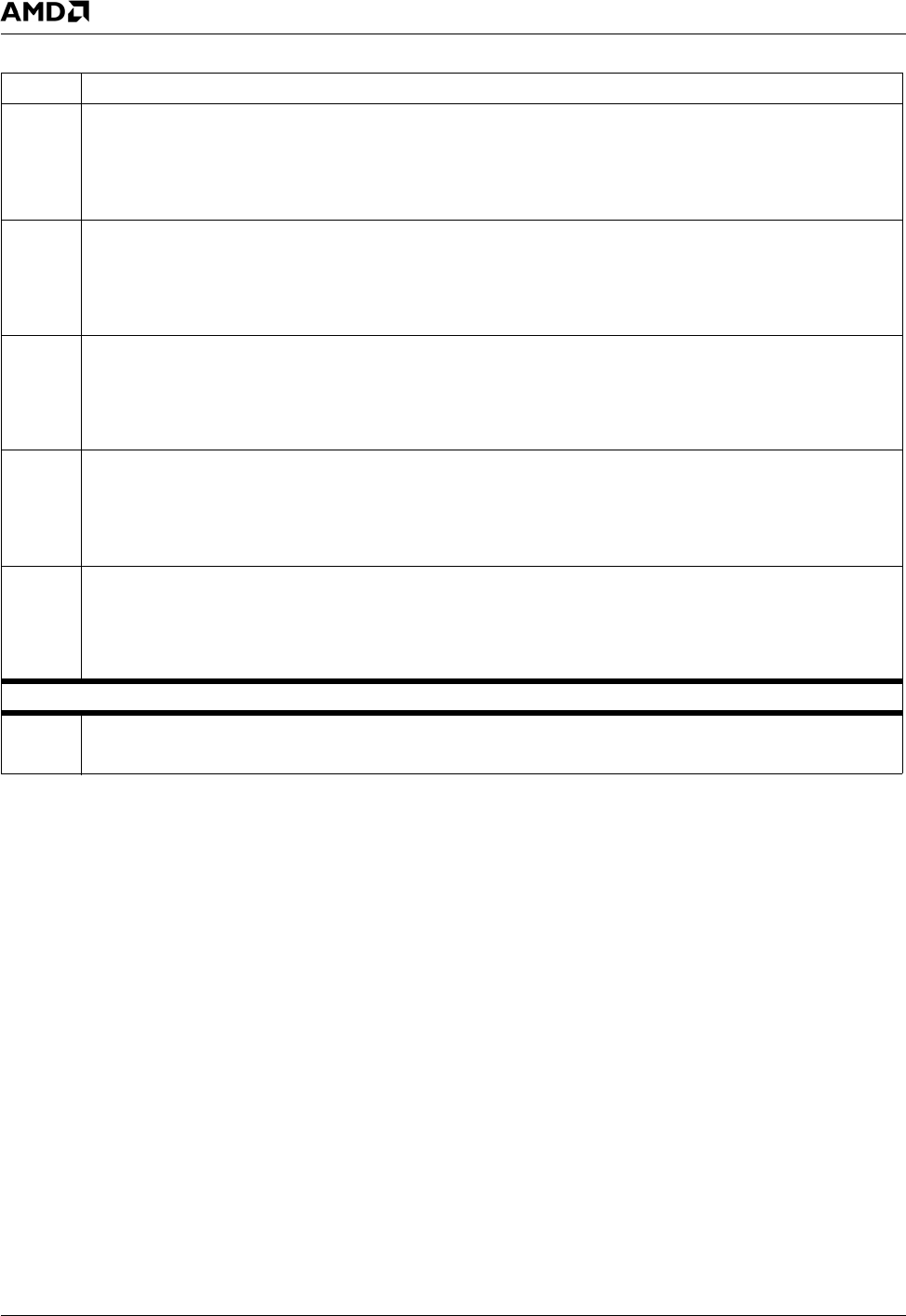

4 EXT_SMI4 SMI Enable. When this bit is asserted, allows EXT_SMI4 to generate an SMI on negative-edge events.

0: Disable.

1: Enable.

Top level SMI status is reported at F1BAR0+00h/02h[10].

Second level SMI status is reported at bits 20 (RC) and 12 (RO).

3 EXT_SMI3 SMI Enable. When this bit is asserted, allow EXT_SMI3 to generate an SMI on negative-edge events.

0: Disable.

1: Enable.

Top level SMI status is reported at F1BAR0+00h/02h[10].

Second level SMI status is reported at bits 19 (RC) and 11 (RO).

2 EXT_SMI2 SMI Enable. When this bit is asserted, allow EXT_SMI2 to generate an SMI on negative-edge events.

0: Disable.

1: Enable.

Top level SMI status is reported at F1BAR0+00h/02h[10].

Second level SMI status is reported at bits 18 (RC) and 10 (RO).

1 EXT_SMI1 SMI Enable. When this bit is asserted, allow EXT_SMI1 to generate an SMI on negative-edge events.

0: Disable.

1: Enable.

Top level SMI status is reported at F1BAR0+00h/02h[10].

Second level SMI status is reported at bits 17 (RC) and 9 (RO).

0 EXT_SMI0 SMI Enable. When this bit is asserted, allow EXT_SMI0 to generate an SMI on negative-edge events.

0: Disable.

1: Enable.

Top level SMI status is reported at F1BAR0+00h/02h[10].

Second level SMI status is reported at bits 16 (RC) and 8 (RO).

Offset 28h-4Fh Not Used Reset Value: 00h

Offset

50h-FFh

The I/O mapped registers located here (F1BAR0+I/O Offset 50h-FFh) can also be accessed at F0 Index 50h-FFh. The pre-

ferred method is to program these registers through the F0 register space. Refer to Table 6-29 "F0: PCI Header/Bridge Con-

figuration Registers for GPIO and LPC Support" on page 198 for more information about these registers.

Table 6-33. F1BAR0+I/O Offset: SMI Status Registers (Continued)

Bit Description