AMD Geode™ SC2200 Processor Data Book 307

Core Logic Module - ISA Legacy Register Space

32580B

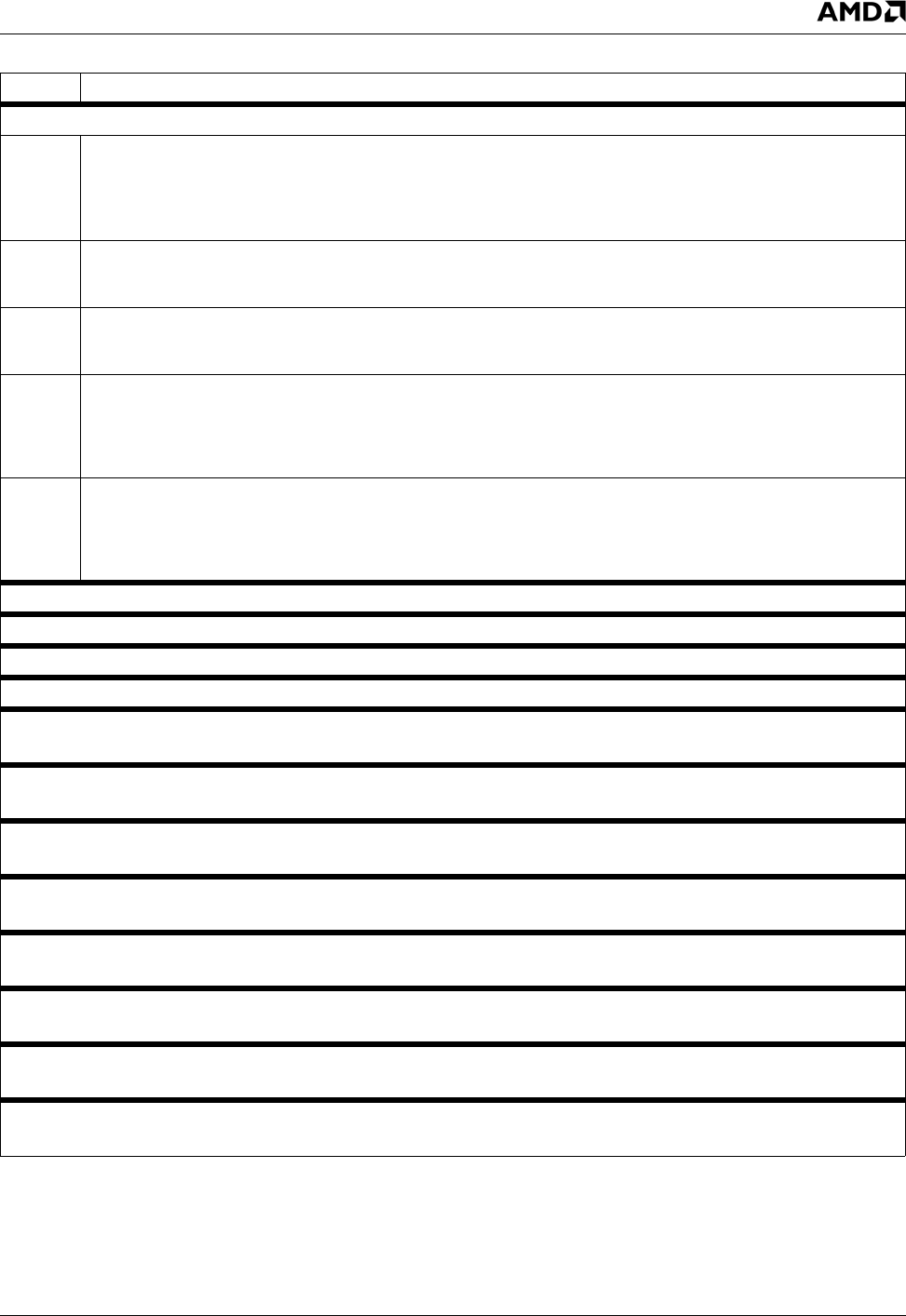

I/O Port 00Bh DMA Channel Mode Register, Channels 3:0 (WO)

7:6 Transfer Mode.

00: Demand.

01: Single.

10: Block.

11: Cascade.

5 Address Direction.

0: Increment.

1: Decrement.

4 Auto-initialize.

0: Disable.

1: Enable.

3:2 Transfer Type.

00: Verify.

01: Write transfer (I/O to memory).

10: Read transfer (memory to I/O).

11: Reserved.

1:0 Channel Number Mode Select.

00: Channel 0.

01: Channel 1.

10: Channel 2.

11: Channel 3.

I/O Port 00Ch DMA Clear Byte Pointer Command, Channels 3:0 (W)

I/O Port 00Dh DMA Master Clear Command, Channels 3:0 (W)

I/O Port 00Eh DMA Clear Mask Register Command, Channels 3:0 (W)

I/O Port 00Fh DMA Write Mask Register Command, Channels 3:0 (W)

I/O Port 0C0h DMA Channel 4 Address Register (R/W)

Not used.

I/O Port 0C2h DMA Channel 4 Transfer Count Register (R/W)

Not used.

I/O Port 0C4h DMA Channel 5 Address Register (R/W)

Not supported.

I/O Port 0C6h DMA Channel 5 Transfer Count Register (R/W)

Not supported.

I/O Port 0C8h DMA Channel 6 Address Register (R/W)

Not supported.

I/O Port 0CAh DMA Channel 6 Transfer Count Register (R/W)

Not supported.

I/O Port 0CCh DMA Channel 7 Address Register (R/W)

Not supported.

I/O Port 0CEh DMA Channel 7 Transfer Count Register (R/W)

Not supported.

Table 6-43. DMA Channel Control Registers (Continued)

Bit Description