164 AMD Geode™ SC2200 Processor Data Book

Core Logic Module

32580B

PIC Interrupt Sequence

A typical AT-compatible interrupt sequence is as follows.

Any unmasked interrupt generates the internal INTR signal

to the CPU. The interrupt controller then responds to the

interrupt acknowledge (INTA) cycles from the CPU. On the

first INTA cycle the cascading priority is resolved to deter-

mine which of the two 8259A controllers output the inter-

rupt vector onto the data bus. On the second INTA cycle

the appropriate 8259A controller drives the data bus with

the correct interrupt vector for the highest priority interrupt.

By default, the Core Logic module responds to PCI INTA

cycles because the system interrupt controller is located

within the Core Logic module. This may be disabled with

F0 Index 40h[0]. When the Core Logic module responds to

a PCI INTA cycle, it holds the PCI bus and internally gener-

ates the two INTA cycles to obtain the correct interrupt vec-

tor. It then asserts TRDY# and returns the interrupt vector.

PIC I/O Registers

Each PIC contains registers located in the standard I/O

address locations, as shown in Table 6-46 "Programmable

Interrupt Controller Registers" on page 313.

An initialization sequence must be followed to program the

interrupt controllers. The sequence is started by writing Ini-

tialization Command Word 1 (ICW1). After ICW1 has been

written, the controller expects the next writes to follow in

the sequence ICW2, ICW3, and ICW4 if it is needed. The

Operation Control Words (OCW) can be written after initial-

ization. The PIC must be programmed before operation

begins.

Since the controllers are operating in cascade mode, ICW3

of the master controller should be programmed with a

value indicating that the IRQ2 input of the master interrupt

controller is connected to the slave interrupt controller

rather than an I/O device as part of the system initialization

code. In addition, ICW3 of the slave interrupt controller

should be programmed with the value 02h (slave ID) and

corresponds to the input on the master controller.

PIC Shadow Register

The PIC registers are shadowed to allow for 0V Suspend to

save/restore the PIC state by reading the PICs write only

registers. A write to this register resets the read sequence

to the first register. The read sequence for the shadow reg-

ister is listed in F0 Index B9h.

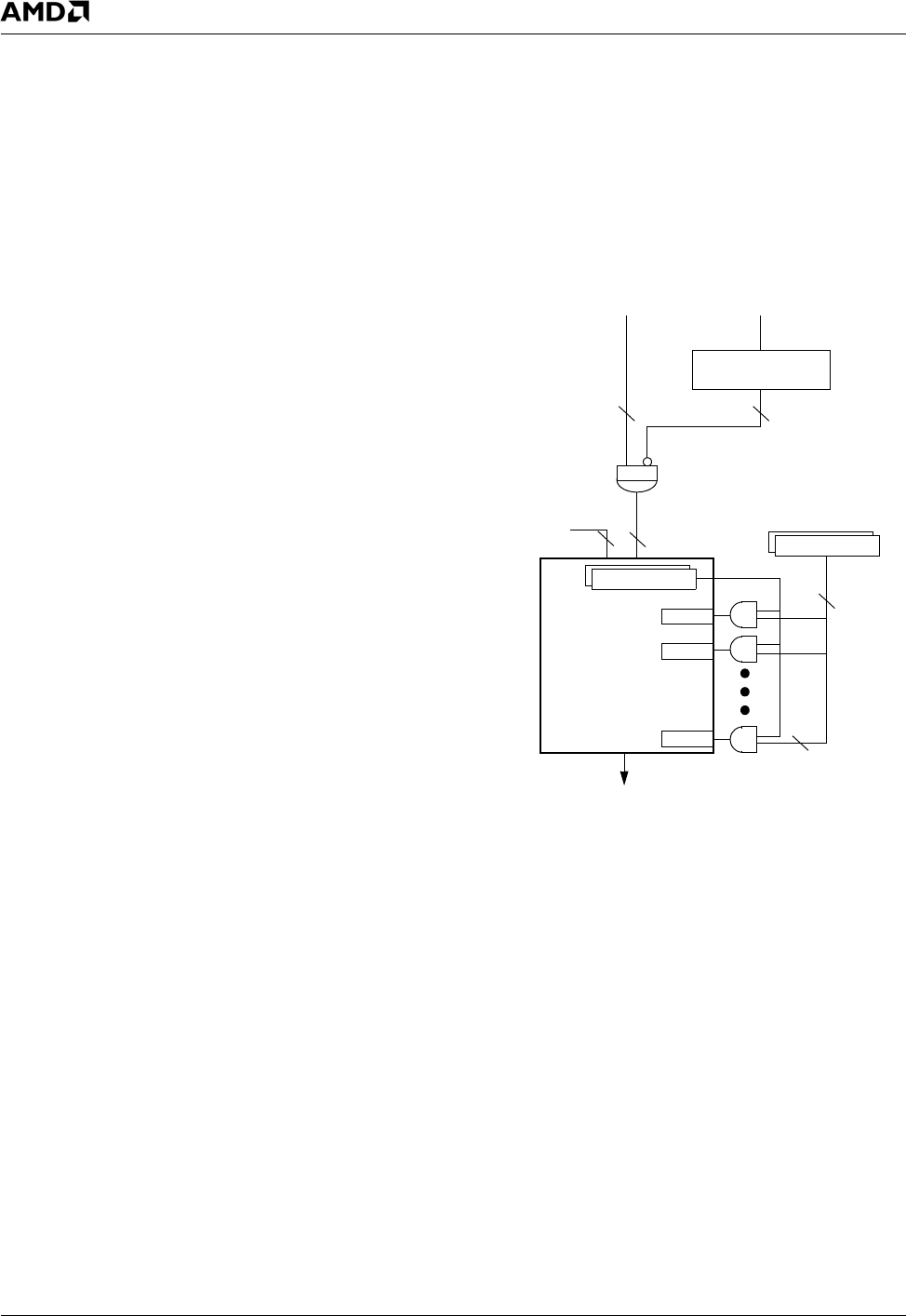

PCI Compatible Interrupts

The Core Logic module allows the PCI interrupt signals

INTA#, INTB#, INTC#, and INTD# (also known in industry

terms as PIRQx#) to be mapped internally to any IRQ sig-

nal with the PCI Interrupt Steering registers 1 and 2, F0

Index 5Ch and 5Dh.

PCI interrupts are low-level sensitive, whereas PC/AT inter-

rupts are positive-edge sensitive; therefore, the PCI inter-

rupts are inverted before being connected to the 8259A.

Although the controllers default to the PC/AT-compatible

mode (positive-edge sensitive), each IRQ may be individu-

ally programmed to be edge or level sensitive using the

Interrupt Edge/Level Sensitivity registers in I/O Port 4D0h

and 4D1h. However, if the controllers are programmed to

be level-sensitive via ICW1, all interrupts must be level-

sensitive. Figure 6-9 shows the PCI interrupt mapping for

the master/slave 8259A interrupt controller.

Figure 6-9. PCI and IRQ Interrupt Mapping

6.2.7 I/O Ports 092h and 061h System Control

The Core Logic module supports control functions of I/O

Ports 092h (Port A) and 061h (Port B) for PS/2 compatibil-

ity. I/O Port 092h allows a fast assertion of the A20M# or

CPU_RST. (CPU_RST is an internal signal that resets the

CPU. It is asserted for 100 µs after the negation of POR#.)

I/O Port 061h controls NMI generation and reports system

status.The Core Logic module generates an SMI for every

internal change of the A20M# state and the SMI handler

sets the A20M# state inside the GX1 module. This method

is used for both the Port 092h (PS/2) and Port 061h (key-

board) methods of controlling A20M#.

PCI INTA#-INTD#

IRQ[15:14,12:9,7:3,1]

Steering Registers

F0 Index 5Ch,5Dh

ICW1

4D0h/4D1h

16

1

12

12 4

Master/Slave

8259A PIC

INTR

IRQ[13,8#,0]

3

Level/Edge

IRQ3

IRQ4

IRQ15

Sensitivity