AMD Geode™ SC2200 Processor Data Book 181

Core Logic Module

32580B

6.2.12.4 IRQ Configuration Registers

The Core Logic module provides the ability to set and clear

IRQs internally through software control. If the IRQs are

configured for software control, they do not respond to

external hardware. There are two registers provided for this

feature:

• Internal IRQ Enable Register (F3BAR0+Memory Offset

1Ah)

• Internal IRQ Control Register (F3BAR0+Memory Offset

1Ch)

Internal IRQ Enable Register

The Internal IRQ Enable register configures the IRQs as

internal (software) interrupts or external (hardware) inter-

rupts. Any IRQ used as an internal software driven source

must be configured as internal.

Internal IRQ Control Register

The Internal IRQ Control register allows individual software

assertion/de-assertion of the IRQs that are enabled as

internal. These bits are used as masks when attempting to

write a particular IRQ bit. If the mask bit is set, it can then

be asserted/de-asserted according to the value in the low-

order 16 bits. Otherwise the assertion/de-assertion values

of the particular IRQ can not be changed.

6.2.12.5 LPC Interface

The LPC interface of the Core Logic module is based on

the Intel Low Pin Count (LPC) Interface specification, revi-

sion 1.0. In addition to the requirement pins that are speci-

fied in the Intel LPC Interface specification, the Core Logic

module also supports three optional pins: LDRQ#, SER-

IRQ, and LPCPD#.

The following subsections briefly describe some sections of

the specification. However, for full details refer to the LPC

specification directly.

The goals of the LPC interface are to:

• Enable a system without an ISA bus.

• Reduce the cost of traditional ISA bus devices.

• Use on a motherboard only.

• Perform the same cycle types as the ISA bus: memory,

I/O, DMA, and Bus Master.

• Increase the memory space from 16 MB to 4 GB to allow

BIOS sizes much greater.

• Provide synchronous design. Much of the challenge of

an ISA design is meeting the different, and in some

cases conflicting, ISA timings. Make the timings

synchronous to a reference well known to component

designers, such as PCI.

• Support software transparency: do not require special

drivers or configuration for this interface. The mother-

board BIOS should be able to configure all devices at

boot.

• Support desktop and mobile implementations.

• Enable support of a variable number of wait states.

• Enable I/O memory cycle retries in SMM handler.

• Enable support of wakeup and other power state transi-

tions.

Assumptions and functionality requirements of the LPC

interface are:

• Only the following class of devices may be connected to

the LPC interface:

— SuperI/O (FDC, SP, PP, IR, KBC) - I/O slave, DMA,

bus master (for IR, PP).

— Audio, including AC97 style design - I/O slave, DMA,

bus master.

— Generic Memory, including BIOS - Memory slave.

— System Management Controller - I/O slave, bus

master.

• Interrupts are communicated with the serial interrupt

(SERIRQ) protocol.

• The LPC interface does not need to support high-speed

buses (such as CardBus, 1394, etc.) downstream, nor

does it need to support low-latency buses such as USB.

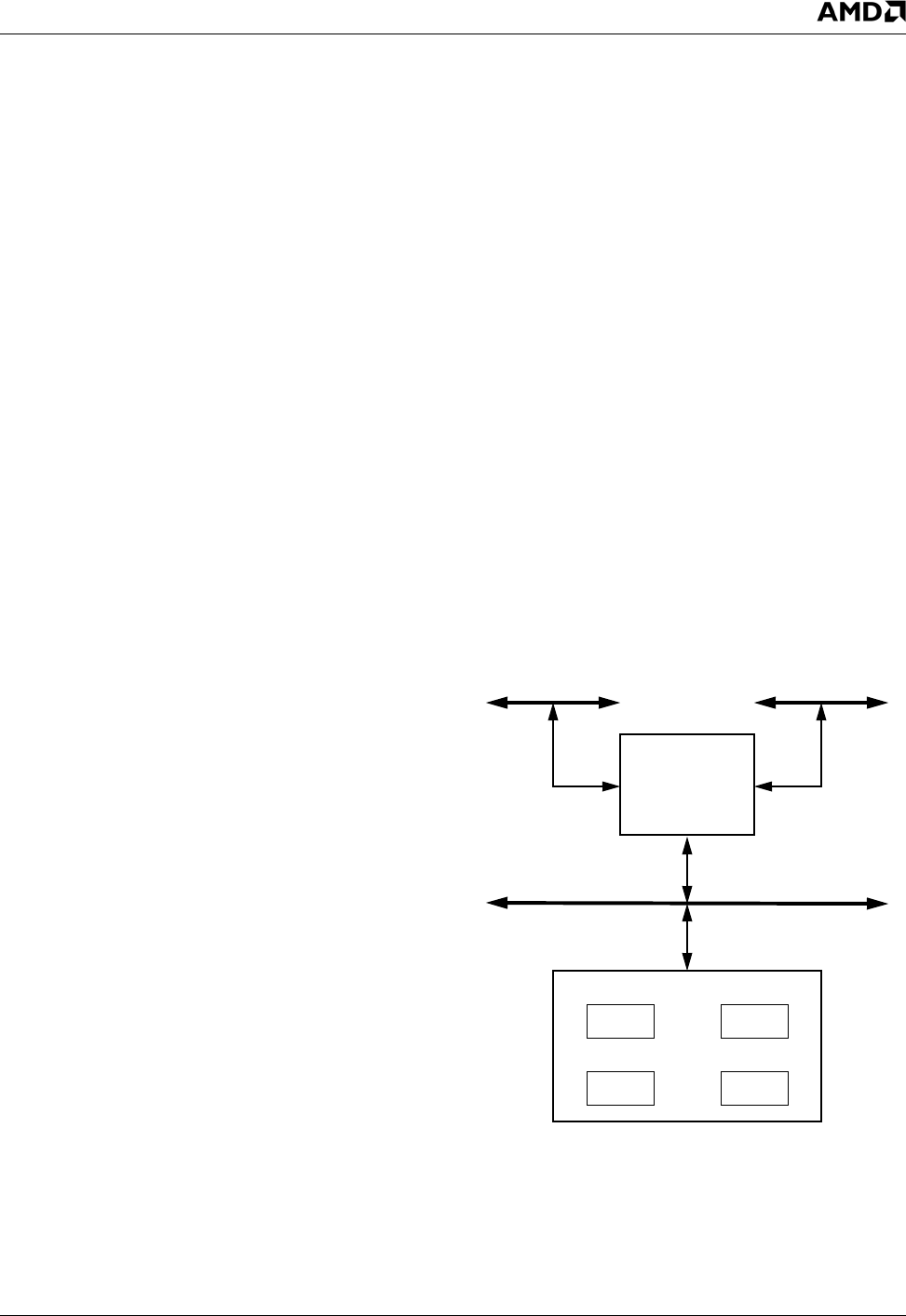

Figure 6-15 shows a typical setup. In this setup, the LPC is

connected through the Core Logic module to a PCI or host

bus.

Figure 6-15. Typical Setup

PCI/Host BusISA (Optional)

LPC

KBC SP

PP FDC

Core Logic

SuperI/O Module

Module