AMD Geode™ SC2200 Processor Data Book 335

Video Processor Module

32580B

7.2.4 VESA DDSC2B and DPMS Support

The Video Processor supports VESA, DDSC2B, and

DPMS standards for enhanced monitor communications

and power management support. This support is provided

via signals DDC_SCL (muxed with IDE_DATA10) and

DDC_SDA (muxed with IDE_DATA9). F4BAR0+Memory

Offset 04h[24, 23, 22] controls the interface.

7.2.5 Integrated DACs

The Video Processor uses a Digital to Analog Converter

(DAC) for CRT display.

To interface directly with the CRT display, the Video Pro-

cessor incorporates triple 8-bit video DACs. The integrated

DACs drive the RED, GREEN and BLUE inputs of the CRT.

Each integrated DAC is an 8-bit current output type which

can run at a clock rate of up to 135 MHz. The integrated

DAC can generate voltage levels from 0 to 1.0V, when driv-

ing 75Ω double-terminated loads.

Differential and integral linearity errors, over full tempera-

ture and voltage ranges, are less than one LSB.

The peak white voltage (V

FR

- full range output voltage),

generated at the DAC, is defined according to the following

formula:

V

FR

= 3.35(V

REF

/ R

SET

)

*

75

where:

V

REF

is the voltage at VREF (either internal bandgap refer-

ence, or externally connected voltage reference).

R

SET

is the value of resistance between SETRES and

AV

SS

(typically 470Ω).

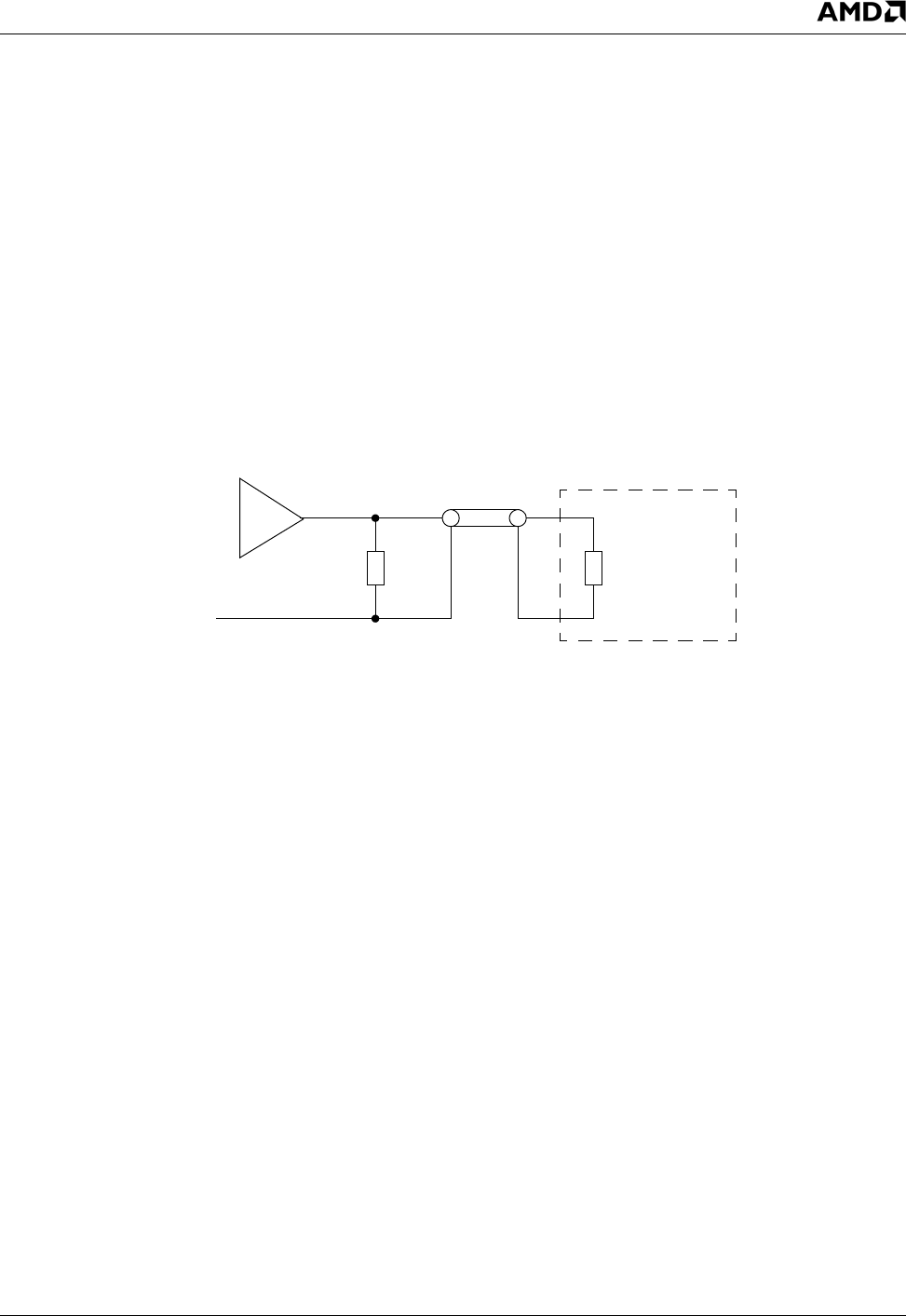

Figure 7-13. DAC Voltage Levels

DAC

AV

SS

CRT

R

L

R

L

Monitor