AMD Geode™ SC2200 Processor Data Book 263

Core Logic Module - SMI Status and ACPI Registers - Function 1

32580B

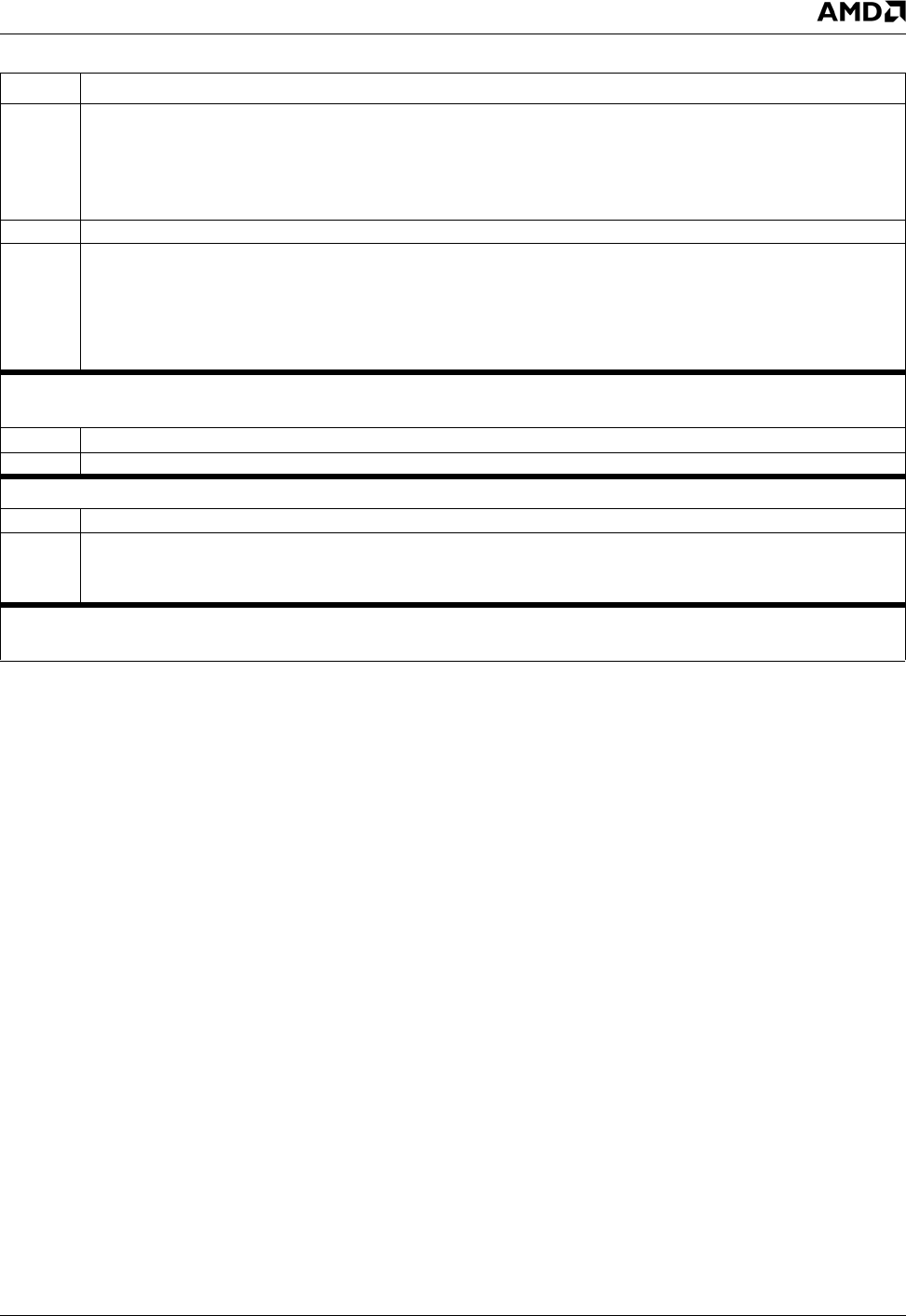

8 THT_SMIEN. Allow SMI generation when the THT_EN bit (F1BAR1+I/O Offset 00h[4]) is set.

0: Disable.

1: Enable. (Default)

Top level SMI status is reported at F1BAR0+I/O Offset 00h/02h[2].

Second level SMI status is reported at F1BAR0+I/O Offset 20h/22h[1].

7:4 Reserved. Must be set to 0.

3:0 SCI_IRQ_ROUTE. SCI is routed to:

0000: Disable 0100: IRQ4 1000: IRQ8 1100: IRQ12

0001: IRQ1 0101: IRQ5 1001: IRQ9 1101: IRQ13

0010: Reserved 0010: IRQ6 1010: IRQ10 1110: IRQ14

0011: IRQ3 0011: IRQ7 1011: IRQ11 1111: IRQ15

For more details see Section 6.2.6.3 "Programmable Interrupt Controller" on page 163.

Offset 1Ch-1Fh PM_TMR — ACPI Timer Register (RO) Reset Value: xxxxxxxxh

Note: This register can also be read at F1BAR0+I/O Offset 1Ch.

31:24 Reserved.

23:0 TMR_VAL. (Read Only) This bit field contains the running count of the power management timer.

Offset 20h PM2_CNT — PM2 Control Register (R/W) Reset Value: 00h

7:1 Reserved.

0 Arbiter Disable. Disables the PCI arbiter when set by the OS. Used during C3 transition.

0: Arbiter not disabled. (Default)

1: Disable arbiter.

Offset 21h-FFh Reserved Reset Value: 00h

The read value for these registers is undefined.

Table 6-34. F1BAR1+I/O Offset: ACPI Support Registers (Continued)

Bit Description