Timers

16-Bit Timer Setup Examples

MN102H75K/F75K/85K/F85K LSI User Manual Panasonic Semiconductor Development Company

119

Panasonic

Timer 5 can output a one-shot pulse. Timer 5 does not operate in STOP mode,

when B

OSC

is off. If you use an external clock, it must be synchronized to B

OSC

.

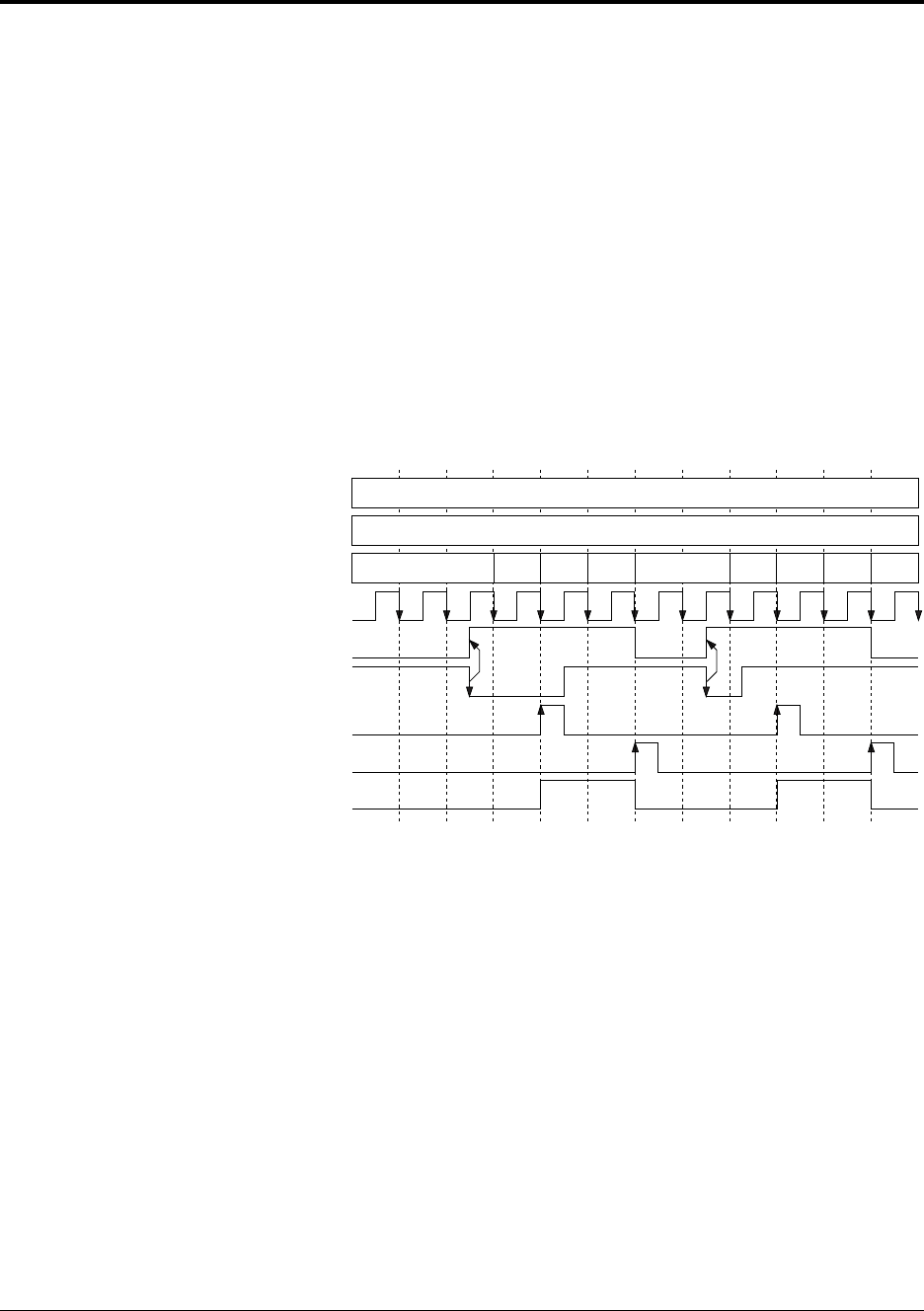

Figure 4-48 shows an example timing diagram for one-shot pulse output. On the

falling edge of TM5IB, the TM5EN flag is set, and counting begins at the start of

the next cycle. Before the count starts, TM5BC is 0, the initial TM5OA output

value is 0, and the R5 (reset) and S5 (set) signals are not asserted. After the count

starts, when it changes from 0 to 1, the S5 signal is asserted. This sets the

TM5OA signal high, and it outputs the one-shot pulse. When the count reaches 3,

TM5BC resets, changing from 3 to 0, and the R5 signal is asserted, causing the

TM5OA signal to go low. Because the TM5ONE bit of the TM5MD register is 1,

and the TM5EN bit is reset, the count stops. The circuit state is now the same as

it was before the TM5IB signal went low. When the TM5IB signal falls again, the

hardware once again sets the TM5EN bit, and the one-shot pulse sequence

repeats.

Figure 4-48 One-Shot Pulse Output Timing (Timer 5)

000000030002000100000003000200010000

0003

0001

TM5CA

TM5CB

TM5BC

B

OSC

/4

TM5EN

TM5IB

S5

R5

TM5OA