Closed-Caption Decoder

Functional Description

Panasonic Semiconductor Development Company MN102H75K/F75K/85K/F85K LSI User Manual

232

Panasonic

9.3.3.1 HSYNC Separator

The HSYNC separator extracts the HSYNC signal from the composite sync

signal using the sampling clock generated by the sync separator clock pulse gen-

erator. This circuit also secures and interpolates the HSYNC signal.

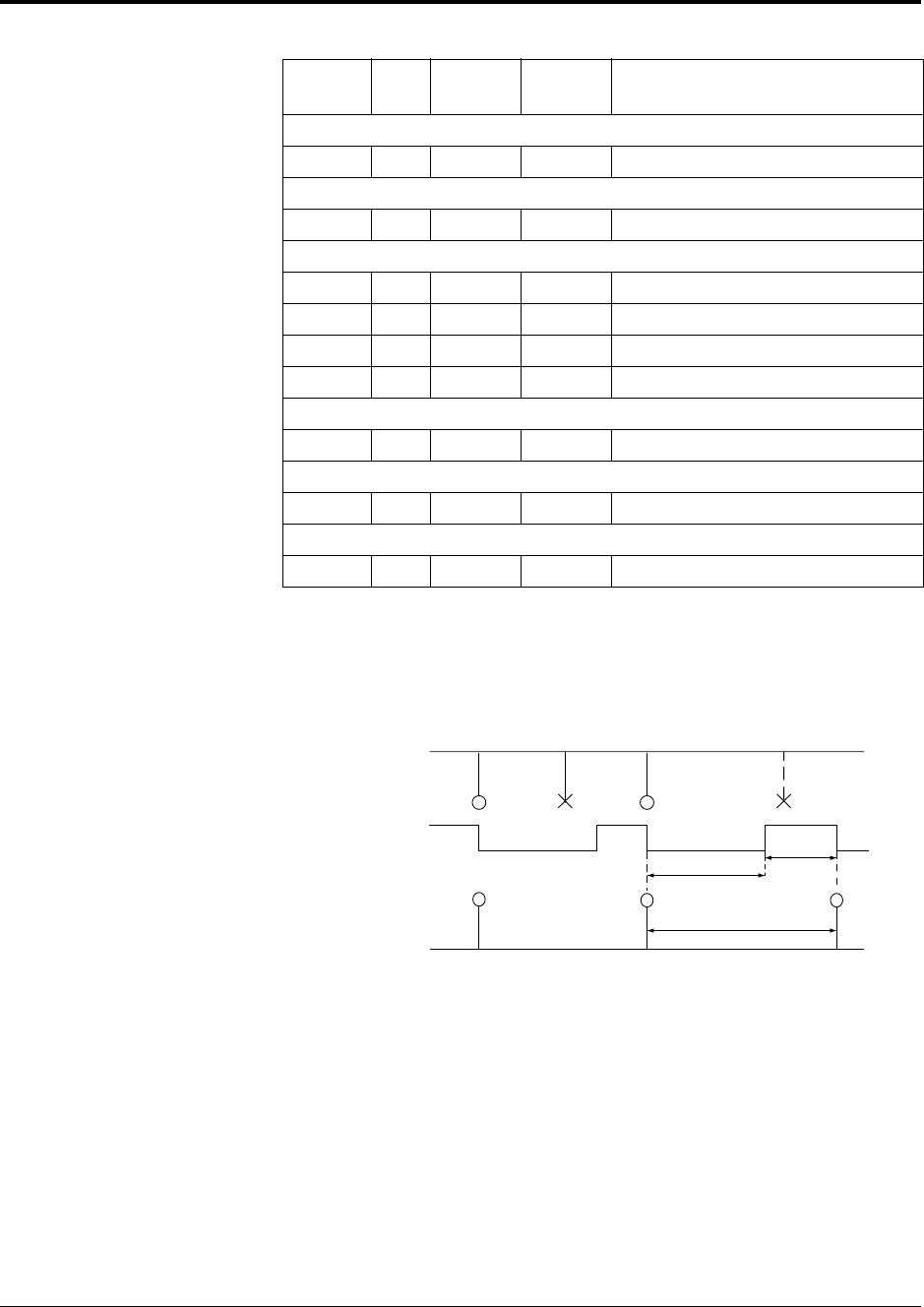

As shown in figure 9-7, noise can cause the HSYNC detection circuit to both

miss HSYNC pulses and add erroneous ones. The HSYNC separator contains a

window circuit to correct these errors. The open and close timing for this window

is set in the HSEP1 and HSEP2 registers, and the unit is the sampling clock for

the HSYNC separator.

The circuit counts a corrected and interpolated HSYNC signal. If the count is

greater than that set in the HLOCKLV register, within the interval set in the

HDISTW register, the HLOCK bit of HVCOND sets to 0, indicating an asyn-

chronous state. This allows the device to determine the quality of the signal.

Table 9-6 Control Registers for Sync Separator Circuit

Register Page

CCDO

Address

CCD1

Address Description

Register for setting the sync separator level

SPLV 244 x’007ECA’ x’007EEA’ Sync separator level set register

Register for controlling the sync separator clock

FQSEL 243 x’007EC2’ x’007EE2’ Frequency select register

Registers for controlling the HSYNC separator

HSEP1 246 x’007ECE’ x’007EEE’ HSYNC separator control register 1

HSEP2 246 x’007ED0’ x’007EF0’ HSYNC separator control register 2

HLOCKLV 246 x’007ED4’ x’007EF4’ Sync separator detection control register 1

HDISTW 247 x’007ED6’ x’007EF6’ Sync separator detection control register 2

Register for controlling the VSYNC separator

VCNT 247 x’007ED8’ x’007EF8’ VSYNC separator control register

Register for controlling the field detection

FIELD 246 x’007ED2’ x’007EF2’ Field detection control register

Register for monitoring the sync separator status

HVCOND 247 x’007EDA’ x’007EFA’ Sync separator status register

Figure 9-7 HSYNC Securement and Interpolation

Interpolated

HSYNC

Missed

HSYNC

Window open

HSEP2 setting

HSEP1 setting

Error HSYNC

resulting from

noise

Detected HSYNC

Window for securing

and interpolating HSYNC

Secured and

interpolated HSYNC