On-Screen Display

OSD Registers

MN102H75K/F75K/85K/F85K LSI User Manual Panasonic Semiconductor Development Company

209

Panasonic

OSD2: OSD Register 2 x’007F08’

SPEXT: Cursor extended mode select

0: Standard mode (16 x 16 pixels)

1: Extended mode (32 x 32 pixels)

GTHT: Graphic tile height select

0: 16 pixels high

1: 18 pixels high

GEXTE: Graphics maximum tiles per line select

0: Maximum 18 tiles

1: Maximum 28 tiles

Setting the YSPLT bit of OSD1

to 1 disables the PRYM bit. With

this setting, you must also set

the TRPT and TRPTF bits to 1.

You can specify transparency for

individual color palettes if

needed.

PRYM: Translucent color control (YM, YS)

0: Normal YS output

1: Don’t output YS during YM output (when the YM color code is not 0)

TRPTF: Translucency control (all layers)

Specifies translucency for color 15 in all palettes.

0: Make color 15 on all palettes translucent

1: Output color 15 as specified

TRPT: Transparency control (all layers)

Specifies transparency for color 0 in all palettes.

0: Make color 0 on all palettes transparent

1: Output color 0 as specified

GCOL[1:0]: Graphics color mode

00: 16-color mode 10: 4-color mode

01: 8-color mode 11: 2-color mode

COLB: Color background control

0: Don’t output color background

1: Output color background

You cannot set VCLK[2:0] to 100

(don’t divide) when the OSC

clock is selected. Only select it

when the clock source is 32

MHz or less.

VCLK[2:0]: VCLK clock select

Divide-by ratio select. The values in parentheses ( ) are applicable when the

oscillator in the OSD1 register is set to the OSC clock (OSCSEL[1:0] = 00).

000: Divide by 4 (12 MHz) 100: Don’t divide (48 MHz)

001: Divide by 3 (16 MHz) 101: Reserved

010: Divide by 2 (24 MHz) 110: Reserved

011: 2/3 division (32 MHz) 111: Reserved

CGPR: Graphics/text layer priority

0: Graphics layer takes priority

1: Text layer takes priority

SOUT/GOUT/COUT: Layer output on/off

SOUT: cursor layer; GOUT: graphics layer; COUT: text layer

0: Don’t output layer

1: Output layer

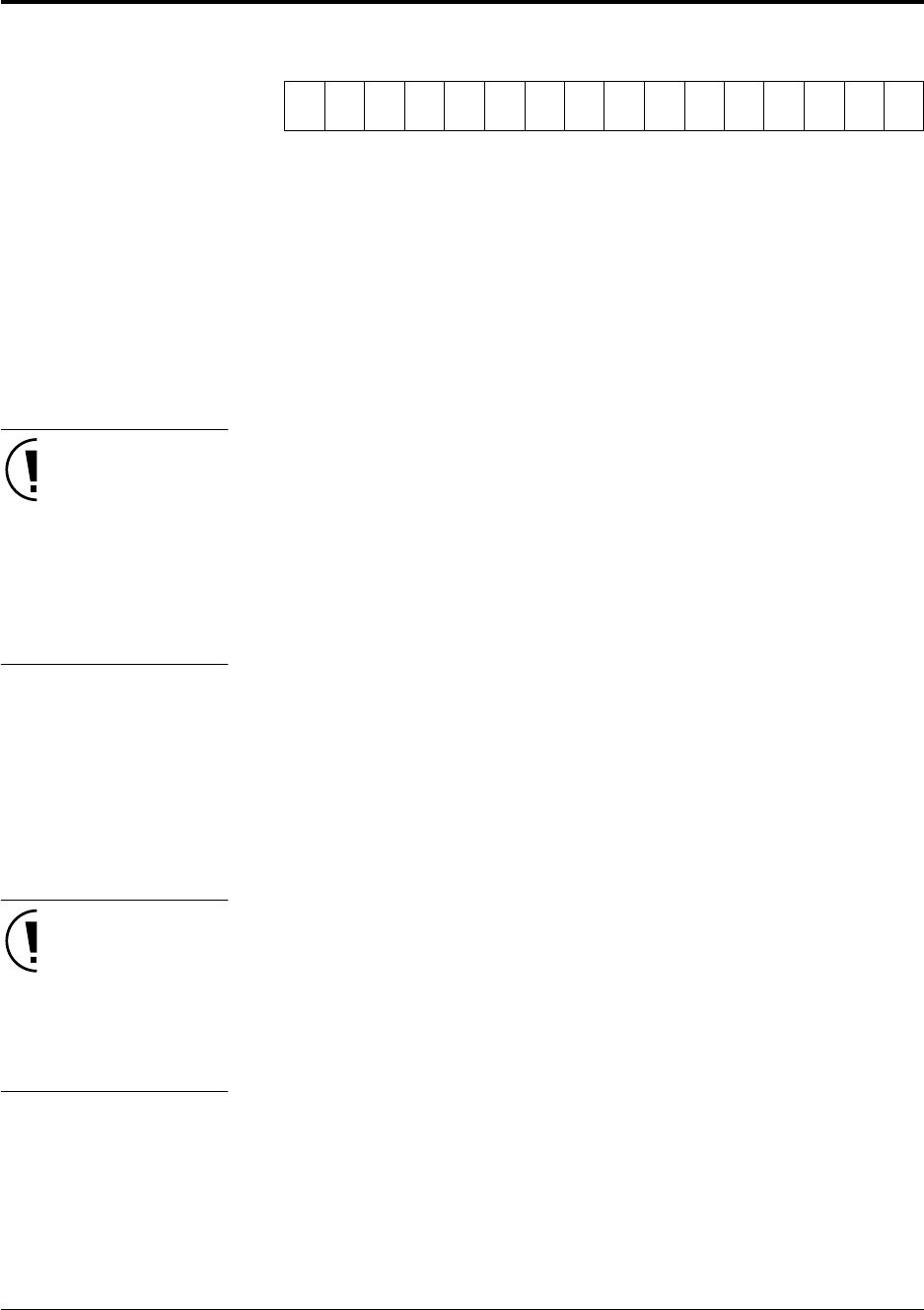

Bit:1514131211109876543210

SPEX

T

GTHT GEXTE PRYM TRPTF TRPT

GCOL

1

GCOL

0

COLB

VCLK

2

VCLK

1

VCLK

0

CGPR SOUT GOUT COUT

Reset:0000000000000000

R/W: R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W R/W