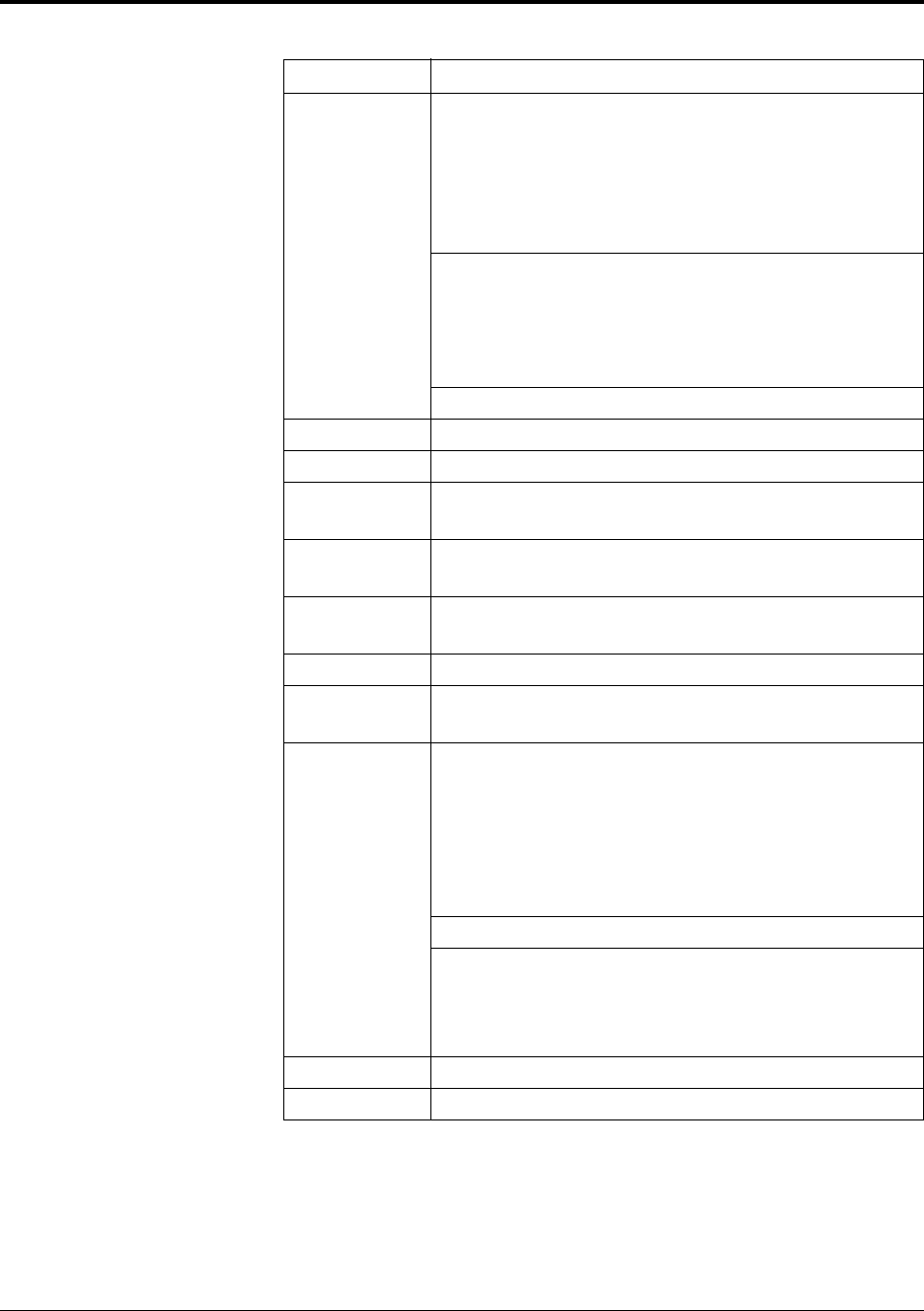

General Description

General Specifications

MN102H75K/F75K/85K/F85K LSI User Manual Panasonic Semiconductor Development Company

27

Panasonic

Timer/counters Four 8-bit timers:

♦ Cascading function (forming 16- or 32-bit timers)

♦ Timer output

♦ Selectable clock source (internal or external)

♦ Serial interface clock generation

♦ Start timing generation for analog-to-digital converter

Two 16-bit timers:

♦ Compare/capture registers

♦ Selectable clock source (internal or external)

♦ PWM and one-shot pulse output

♦ Two-phase encoder input (4x or 1x formats)

16-bit watchdog timer

ROM correction 16 bytes (8-bit × 16)

SYSCLK output SYSCLK or SYSCLK/2

14

(732.42 Hz)

Serial interfaces ♦ Two UART/synchronous serial/I

2

C (master only) interfaces

♦ One I

2

C interface (multimaster; 2-channel with 1 internal circuit)

Analog-to-digital

converter

♦ 8-bit with 12 channels

♦ Automatic scanning

IR remote signal

receiver

♦ Automatic HEAMA / 5-/6-bit detection

♦ 1-bit interrupt

PWM 8-bit with 7 channels (3.3-volt tolerance)

Closed-caption

decoder

♦ 2 channels

♦ Internal sync separator

On-screen display Three-layer format

♦ Text layer: 16 × 18 pixels (16 × 26 in closed caption mode), blink-

ing, outlining, shadowing (foreground and background), shutter

effect, italics (CC mode), underlining (CC mode)

♦ Graphics layer: 16 × 16 / 16 × 18 pixels

♦ Cursor layer: 16 × 16 / 32 × 32 pixels (1 cursor, displaying one

graphic tile)

Color depth: One 16-color palette out of 4096 colors

Dot clock

♦ Internal PLL frequencies: 12, 16, 24, 32 and 48 MHz

♦ External clock: 16–48 MHz

♦ LC blocking oscillator: 16–48 MHz

I/O ports 66(MN102H75K/F75K) / 50(MN102H85K/F85K)

Package 84-pin-QFP(MN102H75K/F75K) / 64-pin-SDIL(MN102H85K/F85K)

Table 1-1 General Specifications

Parameter Specification