Data Integrity and Error Handling

6-14 Intel® 460GX Chipset Software Developer’s Manual

Take the case where processor 1 reads a line from memory and there are no errors, and then does a

write into its cache. Later processor 2 does a read, getting an IWB. The SAC starts a speculative

read for the line before seeing the HITM#. If the data in DRAM has a 2x error on this read the

SDC data buffer will be marked as having a 2x error on this line. In this case, assuming the

speculative read is done (in some cases the HITM# is seen before the memory cycle is attempted,

so no speculative read is done), the IWB data that is written back into memory will be poisoned.

6.9 Data Flow Errors

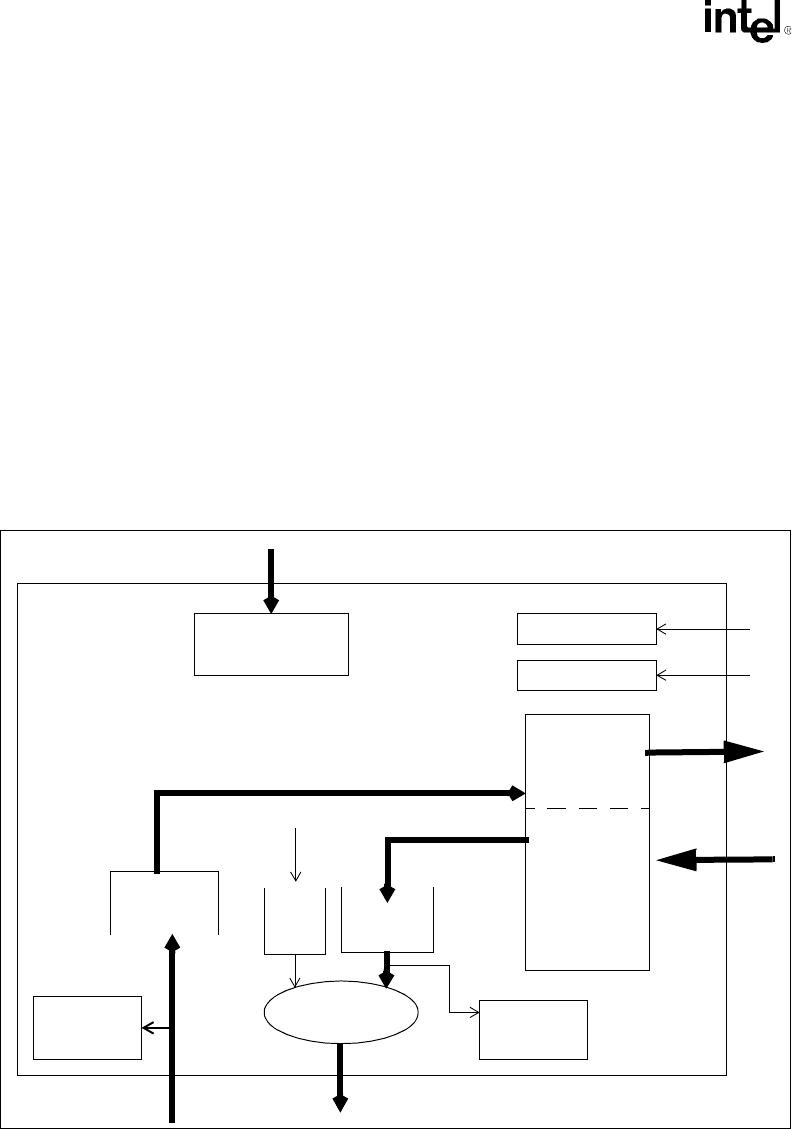

Figure 6-1 and Figure 6-2 show the data flow and errors that are checked. The SDC will report

DRAM errors for either single-bit (S) or double-bit (D) fails. The SDC will never signal that an

error was fatal (causing BINIT#). The processor will handle data that it receives with bad ECC.

The memory will have bad ECC written to it, if incoming data is bad. Data to the SAC will be

handled by the SAC itself. Either the SAC will BINIT# on seeing bad data or it will pass it on to

the xXB via an Expander port.

Figure 6-1. SAC Error Flow on Data

2b BE

From

BIU

16b data,

1Parity

1 parity, 16 data,

2 BE

68b bus

1 parity per

16b of data

1 parity per 18 bits (16 data and 2 BE)

1 parity per 16 bits (16 data)

Expander: To xXBExpander: From xXB

Generate

parity as DP xor

BE0 xor BE1, not

18-way XOR

From

BIU

Check parity.

.

Check parity.

ITID

RETIREMENT

BUS

System Bus

Address parity.

Request parity

.

Bus protocol checking

Pass data with

good/bad parity to

SDC or Expander (peer).

Pass data from SDC

to Expander bus with

good/bad parity.

No checking done.

No checking done.

Check parity on

header and data.

Check for HF.

Check outgoing

parity from data

buffer.

From

SDC

TO

SDC