LPC/FWH Interface Configuration

11-8 Intel® 460GX Chipset Software Developer’s Manual

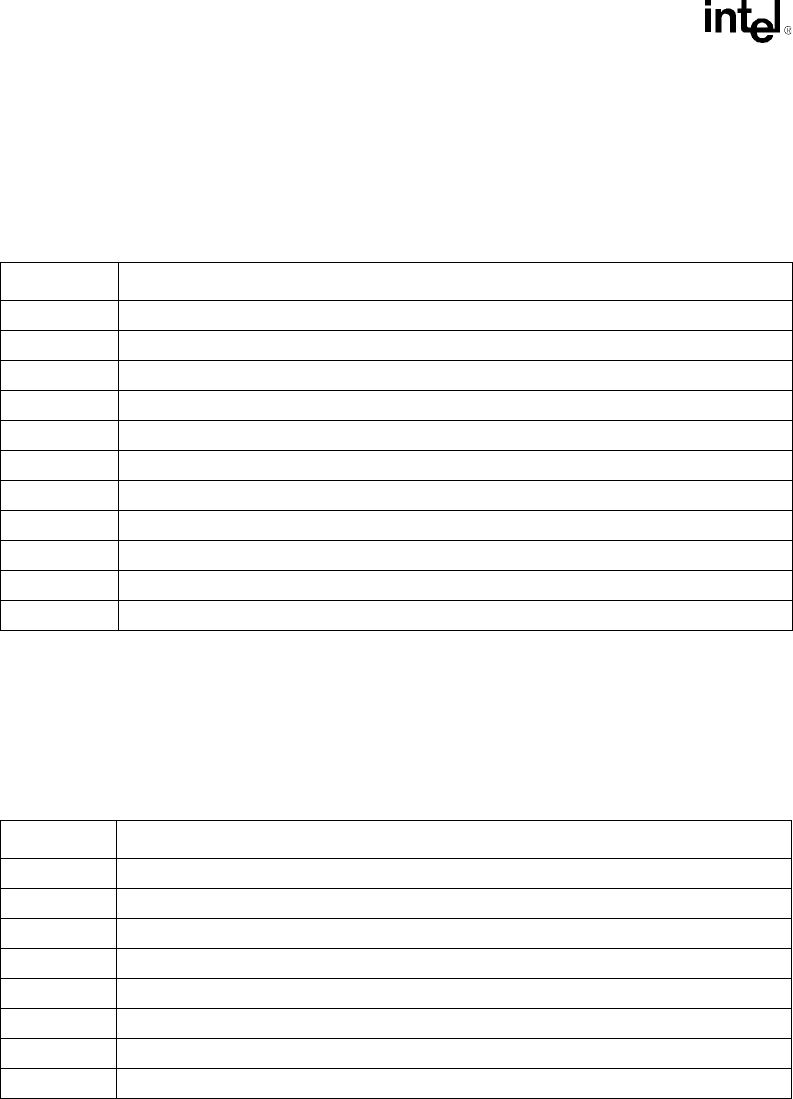

11.1.17 MGPIOC–Muxed GPIO Control (Function 0)

Offset: 84-85h

Default Value: 0500h

Attribute: Read/Write

11.1.18 PDMACFG–PCI DMA Configuration Resister (Function O)

Address Offset: 90-91h

Default Value: 0000h

Attribute: Read/Write

11.1.19 DDMABP–Distributed DMA Slave Base Pointer Registers

(Function 0)

Address Offset: 92-93h (CH0-3), 94-95h (CH5-7)

Default Value: 0000h

Attribute: Read/Write

Bit Description

16:13 Reserved.

12 Reserved. Must be set to ‘1’.

11 Reserved.

10 Reserved. Must be set to ‘1’.

9 Reserved.

8 Reserved. Must be set to ‘1’.

7 Reserved. Must be set to ‘1’.

6 Reserved. Must be set to ‘1’.

5 Reserved. Must be set to ‘1’.

4 Reserved. Must be set to ‘1’.

3:0 Reserved.

Bits Description

15:14 Reserved. Must be set to ‘11’.

13:12 Reserved. Must be set to ‘11’.

11:10 Reserved. Must be set to ‘11’.

9:8 Reserved.

7:6 Reserved. Must be set to ‘11’.

5:4 Reserved. Must be set to ‘11’.

3:2 Reserved. Must be set to ‘11’.

1:0 Reserved. Must be set to ‘11’.