Intel® 460GX Chipset Software Developer’s Manual 14-7

SM Bus Controller Configuration

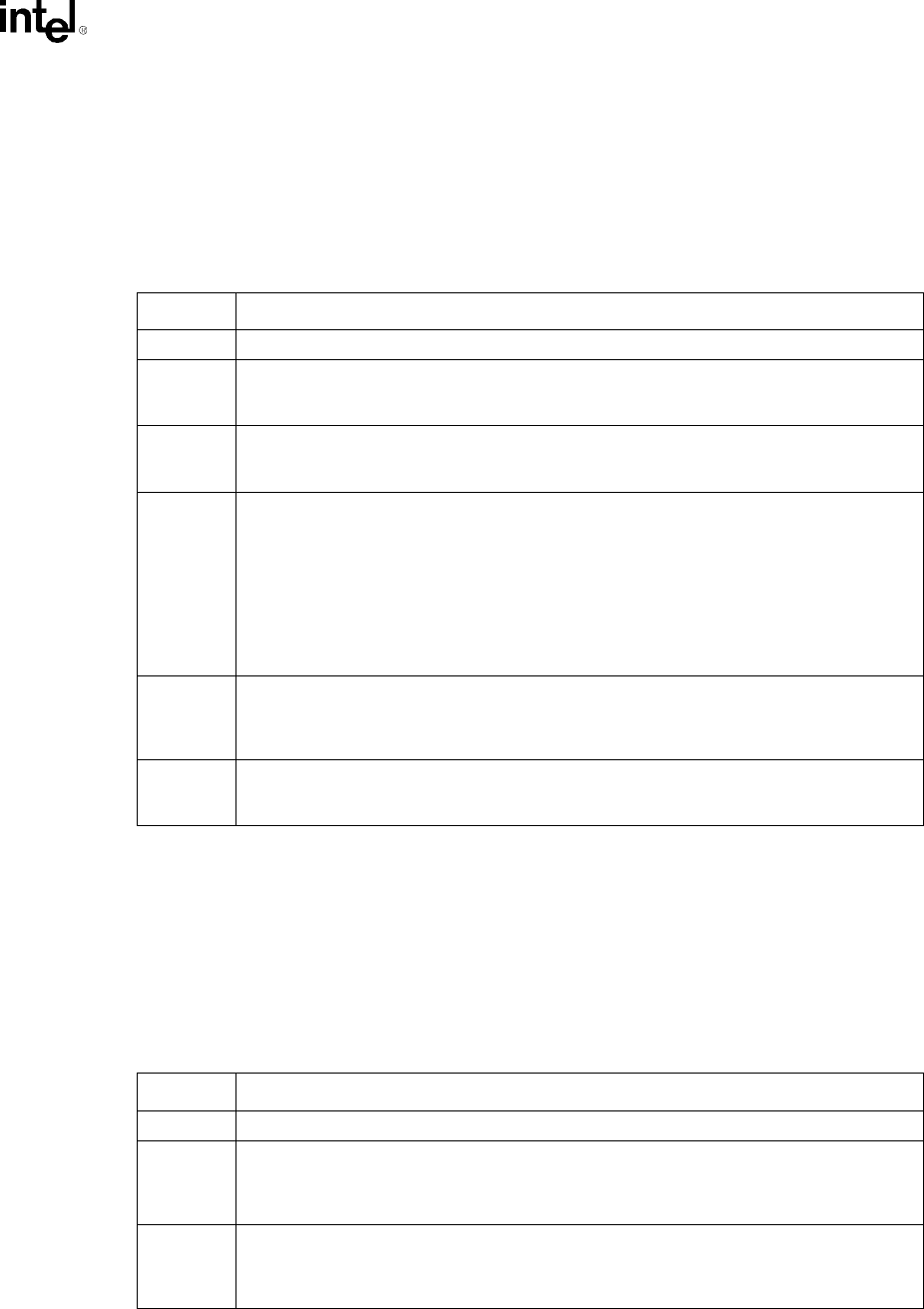

14.3.1 smbhststs–SMBus Host Status Register (I/O)

I/O Address: Base + (00h)

Default Value: 00h

Attribute: Read/Write

This register provides status information concerning the SMBus controller host interface.

14.3.2 smbslvsts–SMBus Slave Status Register (I/O)

I/O Address: Base + (01h)

Default Value: 00h

Attribute: Read/Write

This register provides status information concerning the SMBus controller slave interface.

Bit Description

7:5 Reserved.

4 Failed (FAILED)–R/WC. 1 = Indicates that the source of SMBus interrupt was a failed bus

transaction, set when KILL bit is set (SMBHSTCNT register). 0 = SMBus interrupt not caused by

KILL bit. This bit is only set by hardware and can only be reset by writing a 1 to this bit position.

3 BUS COLLISION(BUS_ERR)–R/WC. 1 = Indicates that the source of SMBus interrupt was a

transaction collision. 0 = SMBus interrupt not caused by transaction collision. This bit is only set

by hardware and can only be reset by writing a 1 to this bit position.

2 Device Error (DEV_ERR)–R/WC. 1 = Indicates that the source of SMBus interrupt was the

generation of an SMBus transaction error. 0 = SMBus interrupt not caused by transaction error.

This bit is only set by hardware and can only be reset by writing a 1 to this bit position.

Transaction errors are caused by:

Illegal Command Field

Unclaimed Cycle (host initiated)

Host Device Time-out

1 SMBus Interrupt (INTER)–R/WC. 1 = Indicates that the source of SMBus interrupt was the

completion of the last host command. 0 = SMBus interrupt not caused by host command

completion. This bit is only set by hardware and can only be reset by writing a 1 to this bit

position.

0 Host Busy (HOST_BUSY)–RO. 1 = Indicates that the SMBus controller host interface is in the

process of completing a command. 0 = SMBus controller host interface is not processing a

command. None of the other registers should be accessed if this bit is set.

Bit Description

7:5 Reserved.

4 Shadow2 Status (SHDW2_STS)–R/WC. 1 = Indicates that the source of SMBus interrupt or

resume event was a slave cycle address match of the SMBSHDW2 port. 0 = SMBus interrupt

not caused by address match to SMBSHDW2 port. This bit is only set by hardware and can only

be reset by writing a 1 to this bit position.

3 Shadow1 Status (SHDW1_STS)–R/WC. 1 = Indicates that the source of SMBus interrupt or

resume event was a slave cycle address match of the SMBSHDW1 port. 0 = SMBus interrupt

not caused by address match to SMBSHDW1 port. This bit is only set by hardware and can only

be reset by writing a 1 to this bit position.