AGP Subsystem

7-8 Intel® 460GX Chipset Software Developer’s Manual

Note: Accesses from an AGP card that are directed to a PCI bus are a system fault and cause a BINIT#

(system reboot). The 460GX chipset does NOT support any access originating from the AGP port

to another PCI bus. This is true for PCI cycles (FRAME# active) as well as AGP cycles.

PCI accesses are always disconnected at a line boundary for writes and a read will at most prefetch

to the end of the line. Therefore each PCI request will have only one translation.

An AGP request may be more than a line in length and therefore could cross a page-boundary. In

that case the request may be broken into 2 parts, each with its own translation and targeted location

(DRAM-space or AGP-space). Each part of the request is handled individually and then the data

recombined before delivering back to the graphics device.

7.2.4 Ordering Rules

The GX will obey AGP ordering rules as spelled out in the AGP specification. The coherent stream

will follow the ordering rules for the type of transaction it is. Low-priority coherent traffic is

treated as being in the same stream as low-priority non-coherent traffic.

7.2.5 Processor Locks and AGP Traffic

AGP non-coherent traffic is not affected by locks on the system bus that target memory or other I/

O devices. The accesses continue to memory independent of whether the LOCK# bit is set on the

bus. However, since legacy code may issue a locked transaction to an AGP device, the GXB must

ensure there is no deadlock in the presence of a lock targeting AGP (see Section 3.6.1 for more

information on processor locks). The lock flow for a single Read-Modify-Write to the AGP bus is

outlined below.

1. An outbound Locked Read request is transferred across the Expander bus.

2. When the locked read request reaches the head of the outbound PCI request queue, it is issued

on the AGP bus with PCI semantics.

3. Once the locked read transaction is complete the read completion is placed in the inbound PCI

transaction queue. At this point the PCI interface establishes a pseudo-lock and begin retrying

all inbound transactions.

4. When the Read completion reaches the head of the PCI inbound PCI transaction queue,

assuming the higher priority queues are empty, it is transferred across the Expander ring. At

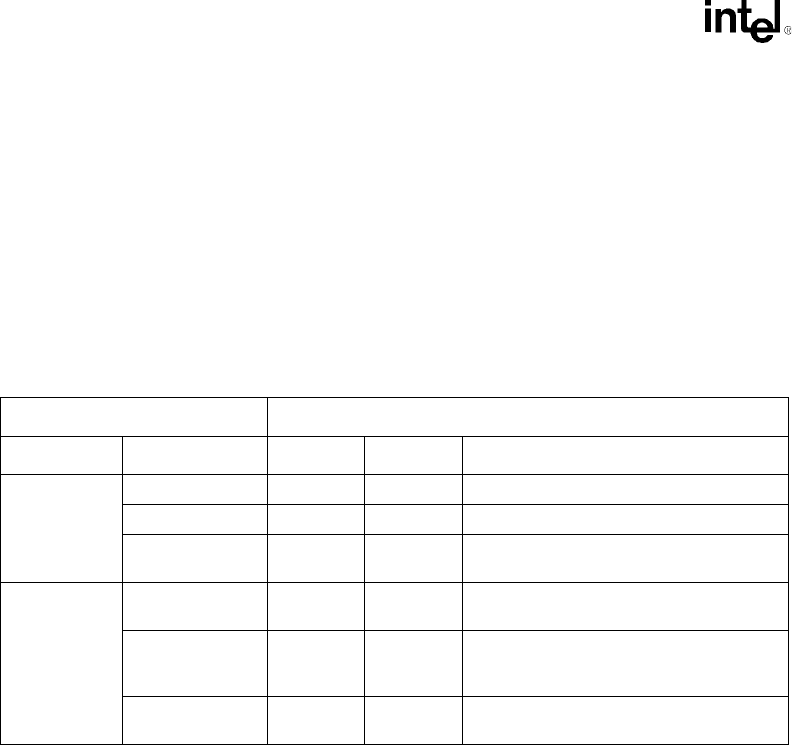

Table 7-1. Coherency for AGP/PCI Streams

Transaction Type System Effect

Traffic Type Address Range Translate Coherent System Action

PCI

(Frame

Active)

AGP-space Yes Always Translated access to memory

DRAM-space No Always Untranslated access to memory

PCI-space No Not

applicable

Peer-to-peer PCI access (THIS IS ILLEGAL

AND CAUSES SYSTEM BINIT#)

AGP

(Pipe# or SB)

AGP-space Yes GART

Sets.

Translated access to memory

DRAM-space No Depends

on Config

bit

Untranslated access to memory

PCI-space No Not

applicable

Peer-to-peer PCI access (THIS IS ILLEGAL

AND CAUSES SYSTEM BINIT#)