Intel® 460GX Chipset Software Developer’s Manual 7-3

AGP Subsystem

7.1.1 GART Implementation

The GX implementation will support 256 MB, 1 GB, or 32 GB (32 GB requires 4 MB pages by the

O.S.) of translation space. This limit is implementation-based not architectural. Each entry in the

GART requires 24 bits for the address, 1 bit for coherency, 1 parity bit and 1 valid bit for a total of

27 bits. The width of each GART entry will be 32 bits. Each entry covers one 4kB (or 4 MB) page.

One megabyte is sufficient to cover 256k entries or a total of 1 GB of translatable space for 4kB

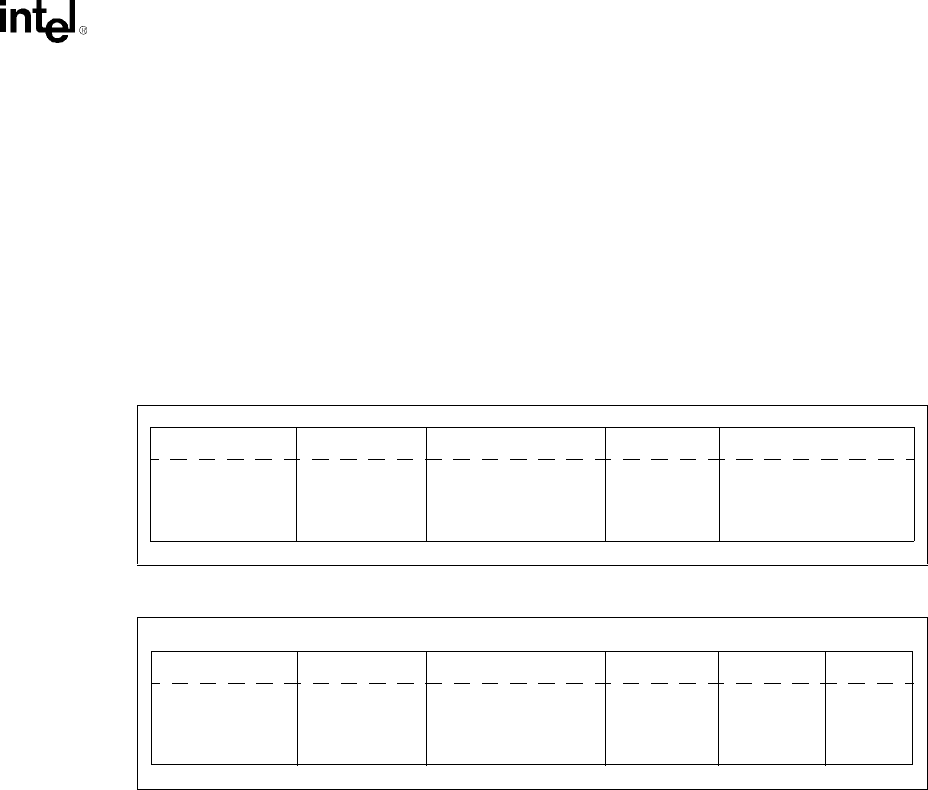

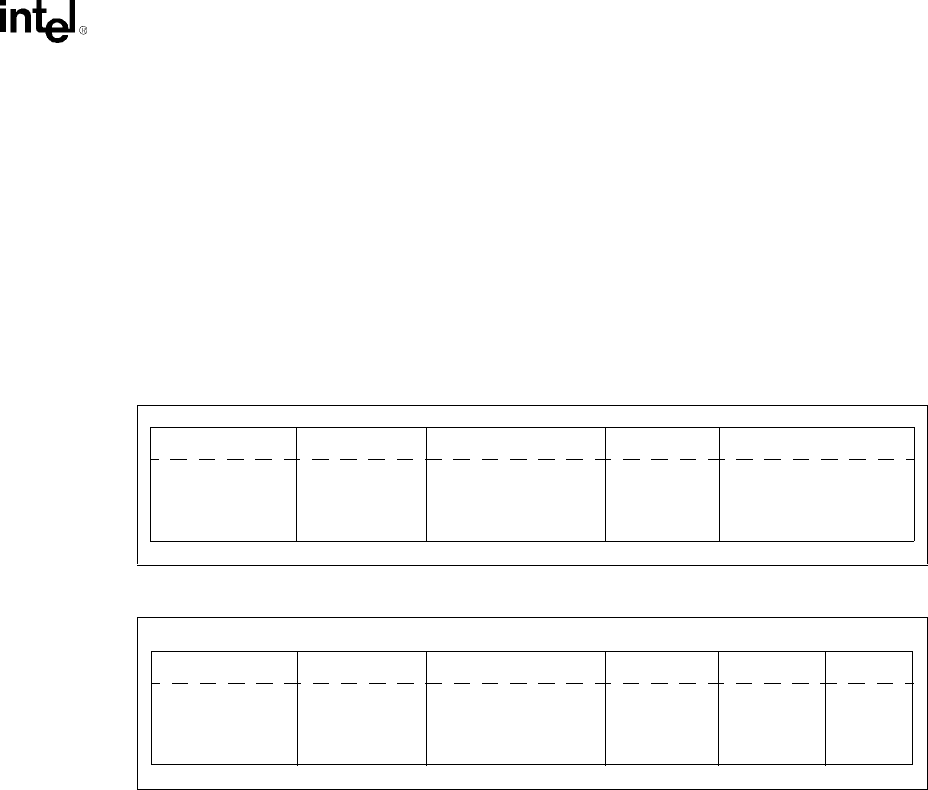

pages. Figure 7-3 and Figure 7-4 show the format of a GART entry. Accesses which hit a GART

entry that does not have the valid bit set are treated as GART misses and the address is passed on

untranslated. Optionally, accesses that hit an entry with the valid bit marked invalid can cause an

error.

The table itself will be kept in SRAM attached to the GXB. It is possible that the table could be in

main memory and the GXB could fetch the translation from memory when it needs a new entry.

Having the GART in local SRAM allows the translations to be done much faster and is a simpler

implementation, since the interface is local and accesses to fetch GART entries don’t compete with

other traffic. A fetch from local SRAM should take 30 ns. or less instead of the roughly 300-500

ns. required to get to DRAM from the GXB.

Both 1 MB and 4 MB SRAMs will be used. To get the 1 MB required, 2 of these parts are required.

For systems that don’t require the full 1 GB translation space, the SRAM scales with the required

space. If 256 MB of translated graphics area were sufficient, then the system could simply populate

256k of SRAM. The GX will support the following sizes of AGP space and SRAM sizes.

• 1 MB of SRAM - 1 GB of AGP space for 4kB pages, requires two 4 MB SRAMs; using 4 MB

pages, the AGP space is still limited to 32 GB.

• 256kB of SRAM - 256 MB of AGP space for 4kB pages, requires two 1MB SRAMs; using 4

MB pages, the AGP space is still limited to 32 GB.

There is no requirement that there be any GART table. If the graphics card doesn’t require

translation, then there is no need of a GART and the SRAM need not be present at all. The GXB

will fully work when there is no SRAM. Of course, in this case, there is no translation so the AGP

card must put out the physical memory address itself.

Figure 7-3. GART Entry Format for 4kB Pages

Figure 7-4. GART Entry Format for 4 MB Pages

1bit

Parity

24bits

New Page

1bit

Val id

1bit

Coherency Bit

Reserved

5bits

1 = Coherent

Must be 0 1=valid

0=invalid

address

0 = Non-coherent

1bit

Parity

1bit

Valid

1bit

Coherency Bit

Reserved

5bits

1 = Coherent

Must be 0 1=valid

0=invalid

10bits

Rsvd.

Must

be 0

0 = Non-coherent

14bits

New Page

address