Intel® 460GX Chipset Software Developer’s Manual 2-49

Register Descriptions

2.6.3.2 I/O (x)APIC Version Register (01h)

The PID contains an I/O (x)APIC version register that identifies the type of I/O (x)APIC it

implements. Software can use this to provide compatibility between different I/O (x)APIC

implementations and their versions. The version register also contains the maximum RTE

.

2.6.3.3 I/O (x)APIC Arbitration ID Register (02h)

This register contains the APIC bus arbitration priority for the PID. This register is loaded

whenever the PID’s (x)APIC ID register is loaded. A rotating priority scheme is used for APIC bus

arbitration. The winner of the arbitration becomes the lowest-priority agent and assumes an

arbitration ID of 0. All other agents except the agent whose ARBID is 15, increment their ARBID

by 1. The agent whose ARBID is 15 will take the winner’s ARBID and will increment it by 1.

ARBIDs are changed (incremented or assumed) only for messages that are successfully

transmitted. A message transmitted successfully means that no CS error or acceptance error was

reported for that message. The PID APIC ARBID is always loaded with the PID APIC ID during a

“INIT-level deassert” message.

Note: Only four bits are required for the APIC ARBID. Bits 27:24 are used for this ID.

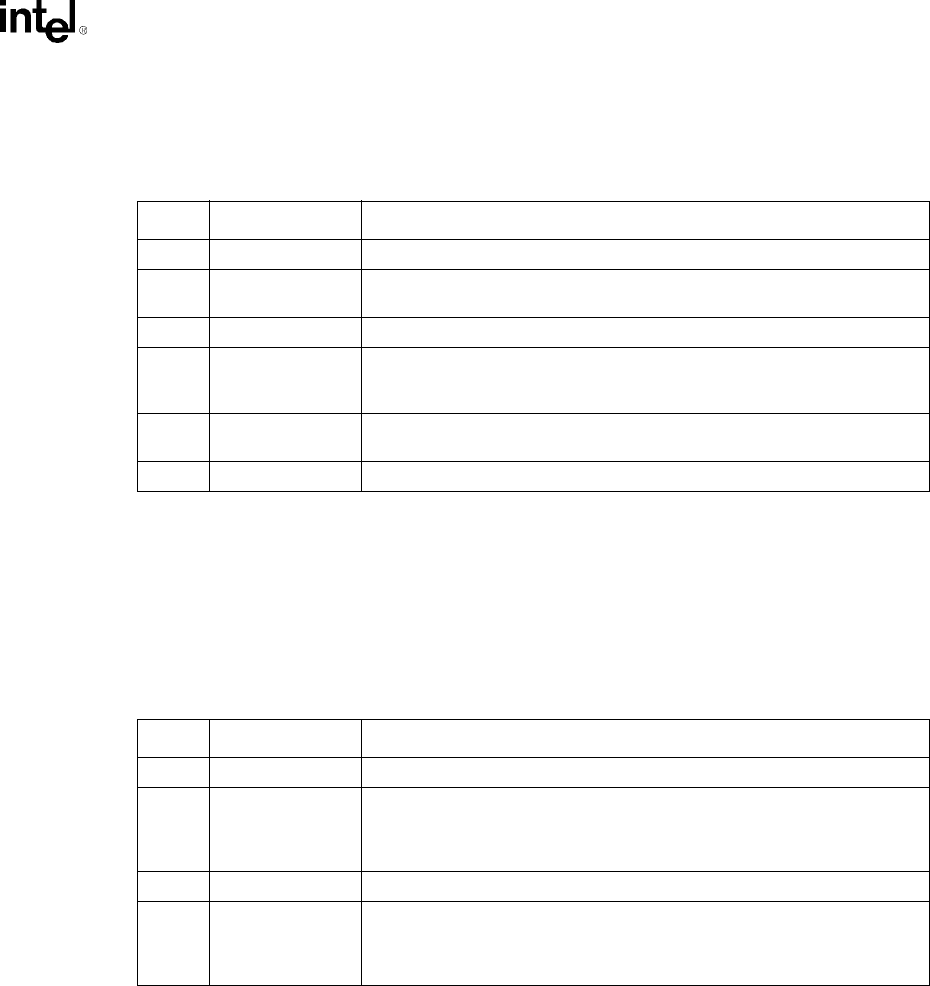

Table 2-7. I/O APIC ID Register Format

Register Offset: 00h Default Value: [00000000h]Attribute: Read/Write

Bit(s) Name Description

31:28 Reserved These four bits are reserved.

27:24 ID[3:0] These four bits provide the APIC ID. This field is used by the I/O APIC unit of

the PID. In SAPIC or compatibility mode of operation, these bits are ignored.

23:16 Reserved These 24 bits are reserved.

15 DT This bit defines the delivery type. A ‘0’ in this field indicates APIC delivery

mechanism. A ‘1’ indicates SAPIC delivery mechanism. This bit reflects the

PICMODE strap pin.

14 LTS Level deassert message support. This bit is always ‘0’ since the PID does not

support “level deassert” messages.

13:0 Reserved Reserved.

Table 2-8. I/O (x)APIC Version Register Format

Register Offset: 01h Default Value: [003F00vvh]Attribute: Read-Only

Bit(s) Name Description

31:24 Reserved These eight bits are reserved

23:16 MAX REDIR This is the entry number (0 being the lowest entry) of the highest entry in the I/

O RT. It is equal to the number of interrupt input pins minus one that the PID

supports. This field is hardwired and is read-only. The PID sets this field to

3FH, indicating that it supports 64 RTEs.

15:8 Reserved These eight bits are reserved.

7:0 VERSION This is a version number that identifies the implementation version of the APIC

or SAPIC units in the PID. This field is hardwired and is read-only. When the

PID powers-up in APIC mode this field will return a value of 13H. When the

PID powers-up in SAPIC mode this field will return a value of 21H.