Intel® 460GX Chipset Software Developer’s Manual 13-7

Universal Serial Bus (USB) Configuration

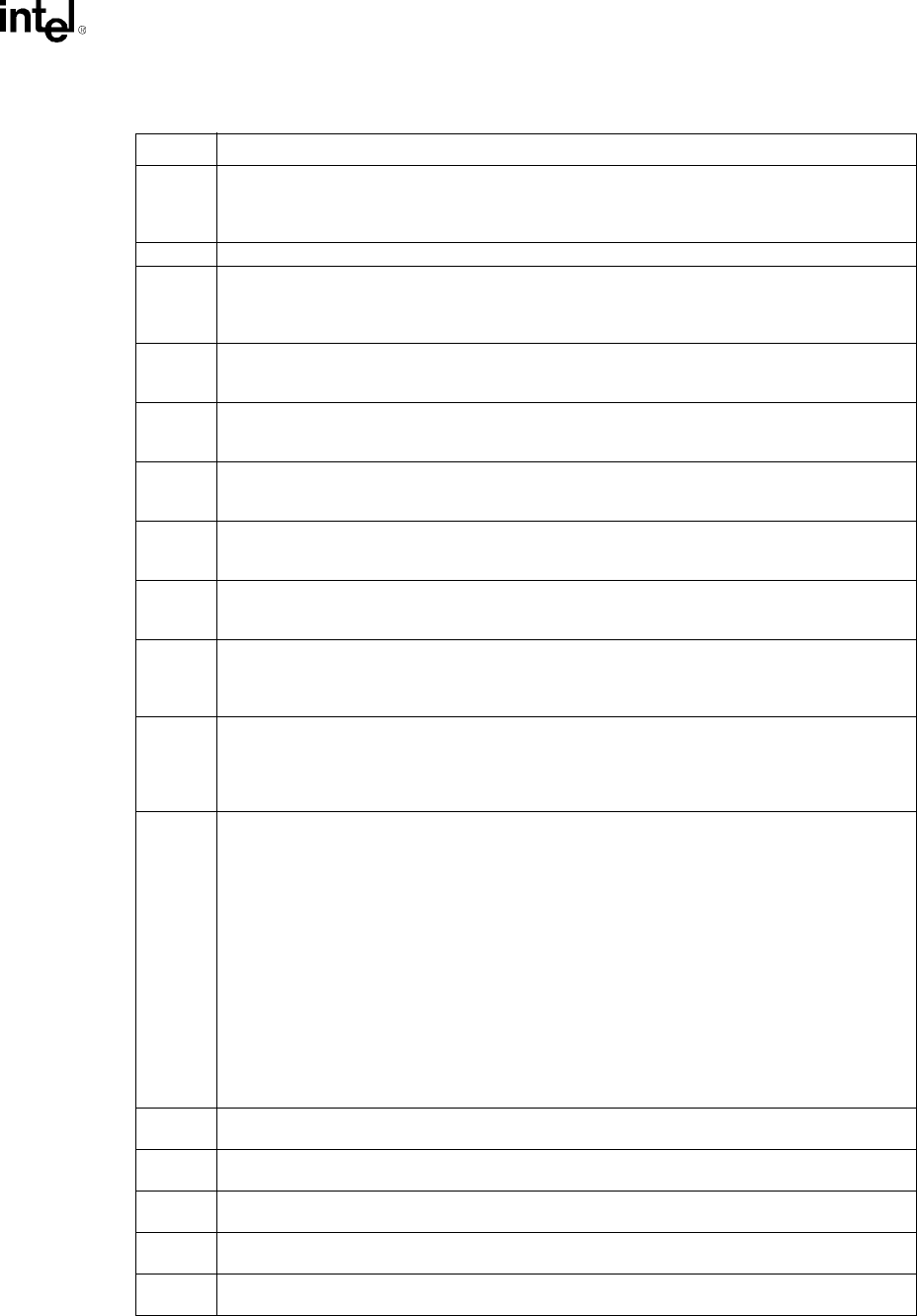

Bit Description

15 End OF A20GATE Pass Through Status (A20PTS)–R/WC. This bit is set to 1 to indicate that the

A20GATE pass-through sequence has ended. This bit will only be set if bit 7 of this register is also

set. Software must use the enable bits to determine the exact cause of an SMI#. Software clears

this bit by writing a 1 to it.

14 Reserved.

13 USB PIRQ Enable (USBPIRQDEN)–R/W. 1 (default) = USB interrupt is routed to PIRQD. 0 = USB

interrupt does not route to PIRQD. This bit prevents the USB controller from generating an

interrupt. Note that it will probably be configured to generate an SMI using bit 4 of this register.

Default to 1 for compatibility with older USB software.

12 USB IRQ Status (USBIRQS)–RO. This bit is set to 1 to indicate that the USB IRQ is active.

Software must use the enable bits to determine the exact cause of an SMI#. Writing a 1 to this bit

will have no effect. Software must clear the IRQ via the USB controller.

11 Trap By 64h Write Status (TBY64W)–R/WC. This bit is set to 1 to indicate that a write to port 64h

occurred. Software must use the enable bits to determine the exact cause of an SMI#. Software

clears this bit by writing a 1 to it.

10 Trap By 64h Read Status (TBY64R)–R/WC. This bit is set to 1 to indicate that a read to port 64h

occurred. Software must use the enable bits to determine the exact cause of an SMI#. Software

clears this bit by writing a 1 to it.

9 Trap By 60h Write Status (TBY60W)–R/WC. This bit is set to 1 to indicate that a write to port 60h

occurred. Software must use the enable bits to determine the exact cause of an SMI#. Software

clears this bit by writing a 1 to it.

8 Trap By 60h Read Status (TBY60R)–R/WC. This bit is set to 1 to indicate that a read to port 60h

occurred. Software must use the enable bits to determine the exact cause of an SMI#. Software

clears this bit by writing a 1 to it.

7 SMI At End Of Pass Through Enable (SMIEPTE)–R/W. 1=Enable the generation of an SMI when

the A20GATE pass-through sequence has ended. 0 (default) = Disable. This may be required if an

SMI is generated by a USB interrupt in the middle of an A20GATE pass through sequence and

needs to be serviced later.

6 Pass Through Status (PSS)–RO. 1 =A20GATE pass through sequence is currently in progress. 0

(default) = Not currently executing the A20GATE pass-through sequence. This bit indicates that

the host controller is executing the A20GATE pass-through sequence. If software needs to reset

this bit, it should set Bit 5 to 0 causing the host controller to immediately end the A20GATE pass

through sequence.

5 A20Gate Pass Through Enable (A20PTEN)–R/W. 1=Enable A20GATE pass through sequence.

0 (default) = Disable. When enabled, the logic will pass through the following A20GATE command

sequence:

Cycle Address Data

Write 64h D1h ( 1 or more) (Starts the Sequence)

Write 60h xxh

Read 64h N/A ( 0 or more)

Write 64h FFh (End of A20GATE Pass Through Sequence)

Any deviation seen in the above sequence will cause the host controller to immediately exit the

sequence and return to typical operation, performing an I/O trap and generating an SMI# if

appropriate enable bits are set.

When enabled, SMI# will not be generated during the sequence, even if the various enable bits are

set. Note that during a Pass-through sequence, the above status bits will not be set for the I/O

accesses that are part of the sequence.

4 Trap/SMI ON IRQ Enable (USBSMIEN)–R/W. 1 = Enable SMI# generation on USB IRQ. 0

(default) = Disable.

3 Trap/SMI On 64h Write Enable (64WEN)–R/W. 1 = Enable I/O Trap and SMI# generation on port

64h write. 0 (default) = Disable.

2 Trap/SMI On 64h Read Enable (64REN)–R/W. 1 = Enable I/O Trap and SMI# generation on port

64h read. 0 (default) = Disable.

1 Trap/SMI On 60h Write Enable (60WEN)–R/W. 1 = Enable I/O Trap and SMI# generation on port

60h write. 0 (default) = Disable.

0 Trap/SMI On 60h Read Enable (60REN)–R/W. 1 = Enable I/O Trap and SMI# generation on port

60h read. 0 (default) = Disable.