Intel® 460GX Chipset Software Developer’s Manual 11-23

LPC/FWH Interface Configuration

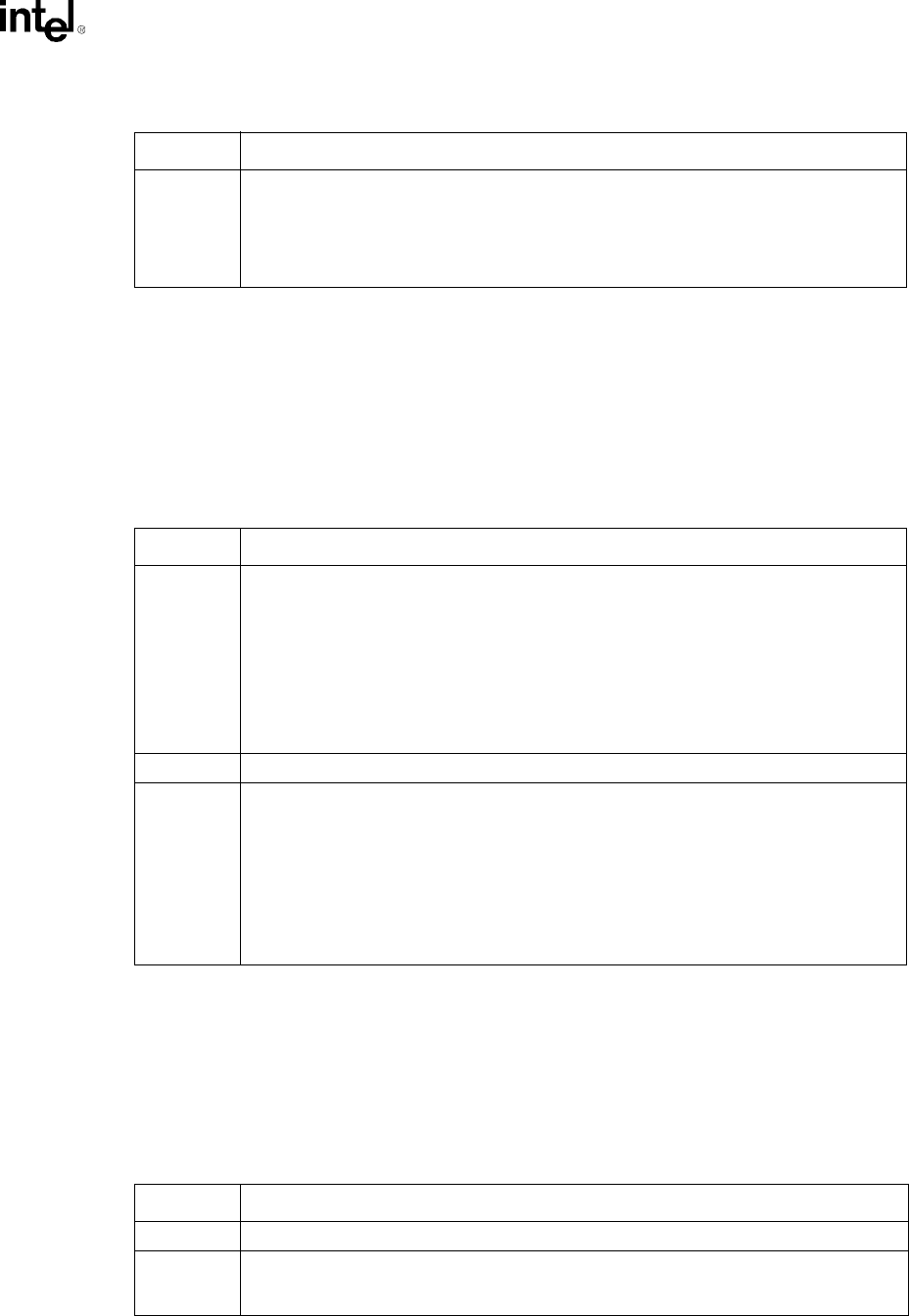

11.2.2.7 Ocw2–Operational Control Word 2 Register (I/O)

I/O Address: INT CNTRL-1–020h; INT CNTRL-2–0A0h

Default Value: Bit[4:0]=undefined; Bit[7:5]=001

Attribute: Write Only

OCW2 controls both the Rotate Mode and the End of Interrupt Mode. Following a CPURST or

ICW initialization, the controller enters the fully nested mode of operation. Both rotation mode and

specific EOI mode are disabled following initialization.

11.2.2.8 Ocw3–Operational Control Word 3 Register (I/O)

I/O Address: INT CNTRL-1–020h; INT CNTRL-2–0A0h

Default Value: Bit[6,0]=0; Bit[7,4:2]=Undefined; Bit[5,1]=1

Attribute: Read/Write

OCW3 serves three important Functions–Enable Special Mask Mode, Poll Mode control, and IRR/

ISR register read control.

Bit Description

7:0 Interrupt Request Mask (Mask [7:0]). When a 1 is written to any bit in this register, the

corresponding IRQx line is masked. For example, if bit 4 is set to a 1, then IRQ4 is masked.

Interrupt requests on IRQ4 do not set channel 4’s interrupt request register (IRR) bit as long is

the channel is masked. When a 0 is written to any bit in this register, the corresponding IRQx is

unmasked. Note that masking IRQ2 on CNTRL-1 also masks the interrupt requests from

CNTRL-2, which is physically cascaded to IRQ2.

Bit Description

7:5 Rotate and EOI Codes. R, SL, EOI - These three bits control the Rotate and End of Interrupt

modes and combinations of the two.

Bits[7:5] Function Bits[7:5] Function

001 Non-specific EOI Cmd 000 Rotate in Auto EOI Mode (Clear)

011 Specific EOI Cmd 111 *Rotate on Specific EOI Cmd

101 Rotate on Non-Spec EOI Cmd 110 *Set Priority Cmd

100 Rotate in Auto EOI Mode (Set) 010 No Operation

* L0 - L2 Are Used

4:3 OCW2 Select. Must be programmed to 00 selecting OCW2.

2:0 Interrupt Level Select (L2, L1, L0). L2, L1, and L0 determine the interrupt level acted upon

when the SL bit is active (bit 6). When the SL bit is inactive, bits [2:0] do not have a defined

Function; programming L2, L1 and L0 to 0 is sufficient in this case.

Bit[2:0] Interrupt Level Bit[2:0] Interrupt Level

000 IRQ 0(8) 100 IRQ 4(12)

001 IRQ 1(9) 101 IRQ 5(13)

010 IRQ 2(10) 110 IRQ 6(14)

011 IRQ 3(11) 111 IRQ 7(15)

Bit Description

7 Reserved. Must be 0.

6 Special Mask Mode (SMM). If ESMM=1 and SMM=1, the interrupt controller enters Special

Mask Mode. If ESMM=1 and SMM=0, the interrupt controller is in normal mask mode. When

ESMM=0, SMM has no effect.