IFB Usage Considerations

10-8 Intel® 460GX Chipset Software Developer’s Manual

Software at this stage needs to determine if at least one of the above modes is supported by the

drive. Software should initially determine a drive’s best PIO w/IORDY capability (PIO4 w/IORDY

or PIO3 w/IORDY) initially. If these PIO w/IORDY modes are not supported, the drive should

determine the PIO2 mode support with IORDY or PIO2 mode support without IORDY. Otherwise,

Compatible timings should be applied to the drive.

The drive’s PIO w/IORDY mode capability is specified in the IDENTIFY_DRIVE buffer, Words

64 and 68. Software must first check to see that the Words 64-70 are valid before determining the

drive’s PIO w/IORDY drive capability.

The drive’s PIO2 mode capability and current configuration are specified in the

IDENTIFY_DRIVE buffer, Word 51.

To determine the drive’s best PIO capability ensure that the drive reports the capability and is able

to transfer at the target cycle time:

Note: The cycle times associated with the various timing modes are defined by the ATA Specification. A

drive that reports a given PIO capability must be capable of supporting the minimum cycle time for

that mode.

Note: If a drive does not report a PIO cycle time that is consistent with the Target PIO Cycle Time, a

slower speed should be chosen.

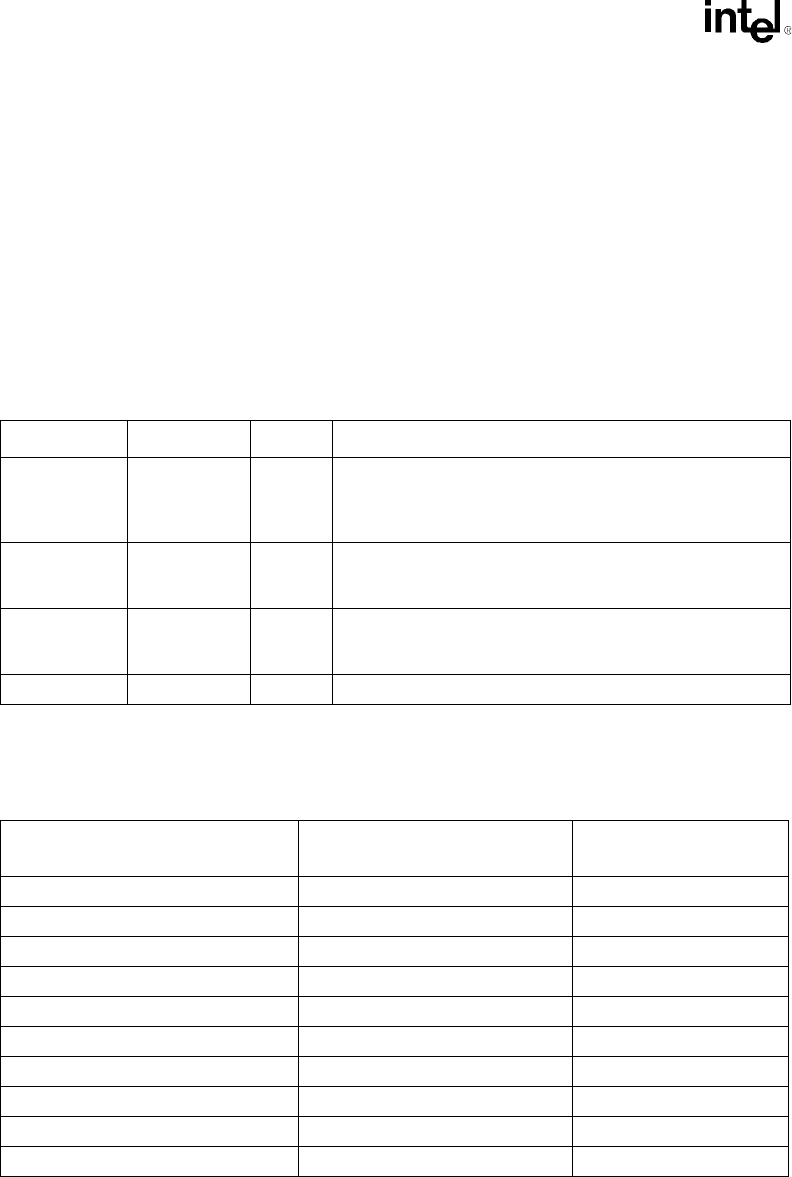

Table 10-5. Identify Device Information Used for Determining PIO Drive Capabilities

Capability Word Offset Bits Field

PIO 51 15:8 PIO Data Transfer Cycle Timing Mode Supported

00h: PIO0

01h: PIO1

02h: PIO2

PIO, DMA 53 1 Field Validity

0: the fields reported in words 64-70 are not valid

1: the fields reported in word 64-70 are valid

PIO 64 7:0 Advanced Flow Control PIO Transfer Modes Supported

bit 0: PIO3 (w/IORDY Flow Control)

bit 1: PIO4 (w/IORDY Flow Control)

PIO 68 15:0 Minimum PIO Transfer Cycle Time with IORDY Flow Control

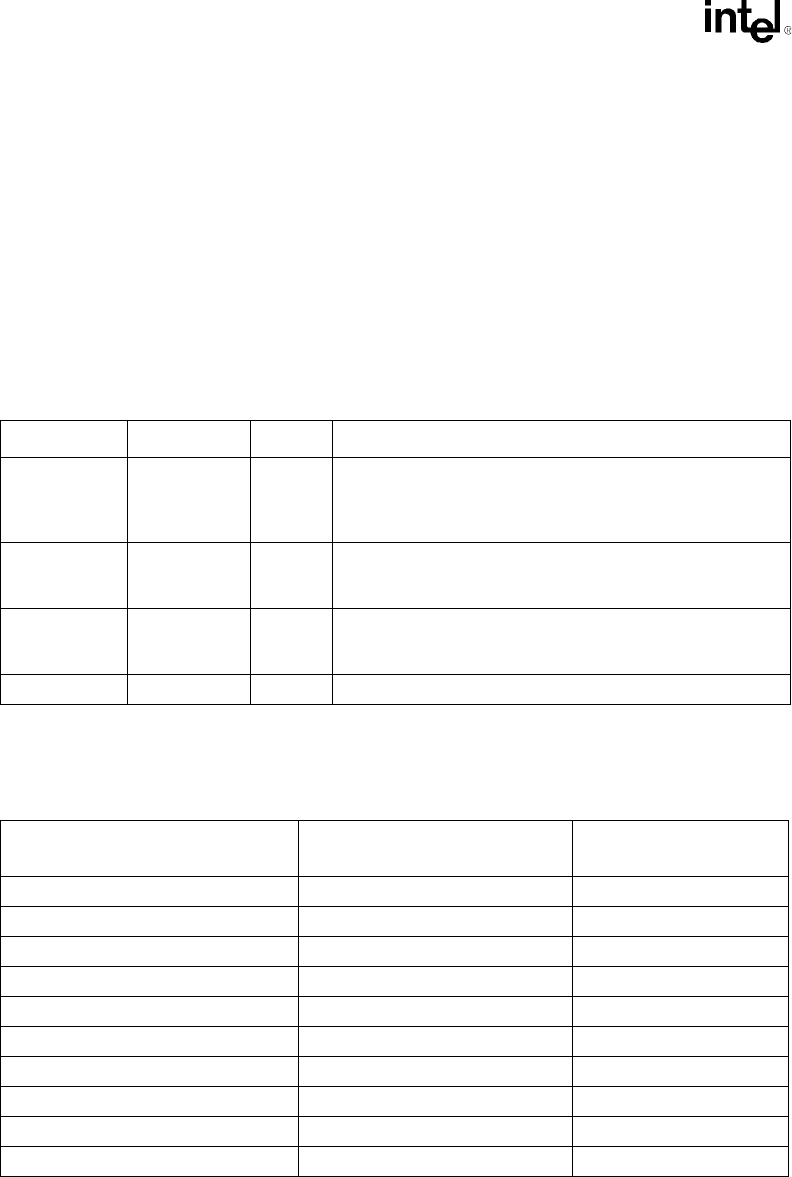

Table 10-6. Drive PIO Capability as a Function of Cycle Time

Drive’s Reported PIO Mode Setting

Drives Reported PIO

Cycle Time

Drive’s Best PIO Mode

PIO4 t <= 120ns PIO4

PIO4 120 < t <= 180ns PIO3

PIO4 180 < t <= 240ns PIO2

PIO4 t > 240ns PIO0/Compatible

PIO3 t <= 180ns PIO3

PIO3 180 < t <= 240ns PIO2

PIO3 t > 240ns PIO0/Compatible

PIO2 N/A (drive must support t<= 240ns) PIO2

PIO1 N/A PIO0/Compatible

PIO0/Compatible N/A PIO0/Compatible